Hi Team,

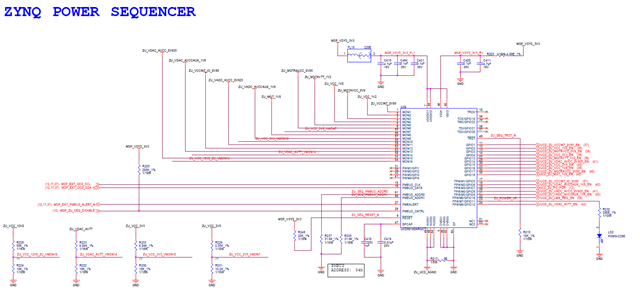

We have a custom board, which has UCD90160 power sequencer to monitor and sequence the power rails of FPGA. In the new build of custom board, we have used a UCD90160A device which is pin to pin replacement device for UCD90160 .

We have a system file(.tifsp file) of the design which has UCD90160 (added in the attached zip file for your reference).

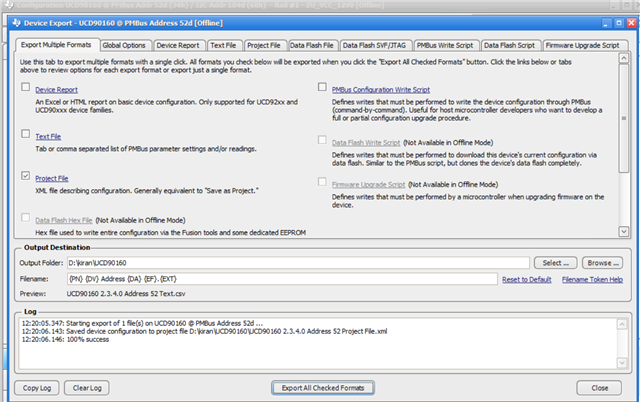

From this system file we exported the project file (XML file) of UCD90160 alone in the offline mode using Fusion digital tool as shown in below image (XML file is in attached zip file for your reference)

In the new build of custom board which has UCD90160A, we imported this XML file to configure the UCD.

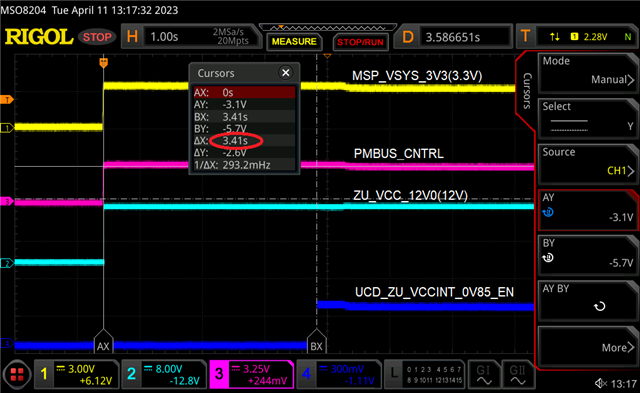

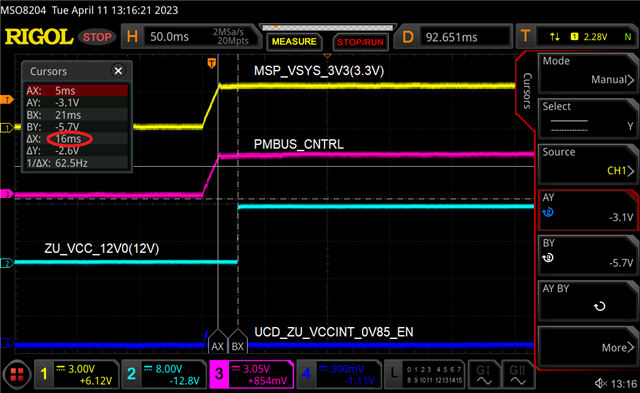

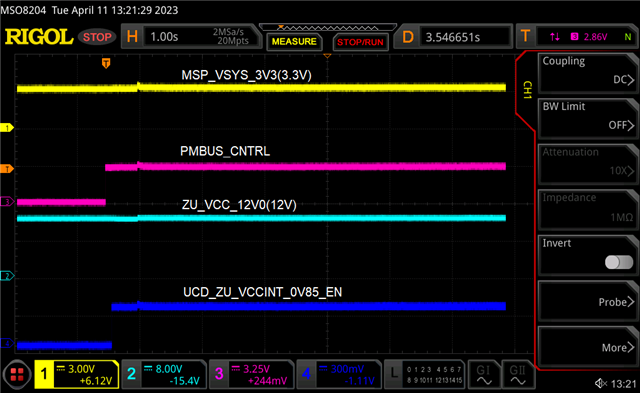

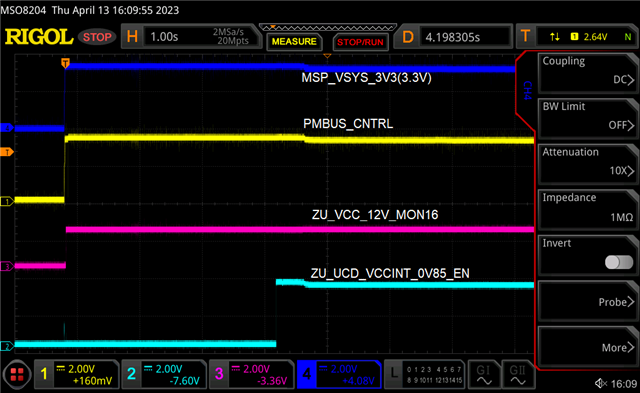

After successful import and configured, When the board is powered on, it is taking around 3.5 seconds to complete the power up the FPGA rails which was not observed in the previous boards which was used to power on immediately. When started debugging the issue we found out that after monitoring the first voltage rail (i.e is 12V in our design which directly from a external supply), the enable to the second rail in sequence was delayed by around 3.3 seconds by the UCD.

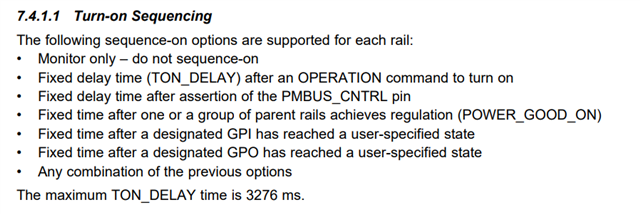

From the datasheet of UCD90160A, the max TON_DELAY for a rail that can be configured is 3276ms as shown below, which is almost matching the delay we observed as mentioned above.

By any chance UCD90160A is entering to Maximum TON_DELAY state to turn on the second rail even though we have not configured the TON_DELAY of 3276ms?

This delay in power up is observed only when the board is powered fresh. When the UCD is controlled through PMBUS_CNTRL pin to turn off and turn on the sequence without power off the external supplies, the UCD is behaving properly and we can observe the power up of FPGA rails happing immediately upon asserting the PMBUS_CNTRL without such huge delay.

Can we know what can be the factors causing such issues?

Here is the schematics of the UCD9016A for your reference

--

Thanks in Advance

Kiran