Hi team,

If EN is driven High before the off-sequence is completed, will the on-sequence resume after the off-sequence ends?

Or will the on-request be ignored?

Best Regards,

Best Regards,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

If EN is driven High before the off-sequence is completed, will the on-sequence resume after the off-sequence ends?

Or will the on-request be ignored?

Best Regards,

Best Regards,

Hi,

Thank You for using E2E. The ON-request on the enable pin is ignored until the PMIC completes the power-down sequence.

Thanks,

Brenda

Hi Brenda,

When does the PMIC complete the power-down sequence?

If EN remains high, will it automatically enter the power-up sequence after completing the power-down sequence?

Do I have to turn off VSYS to reboot the PMIC?

Best Regards,

Hi,

Here are the responses to the questions in the previous message:

When does the PMIC complete the power-down sequence?

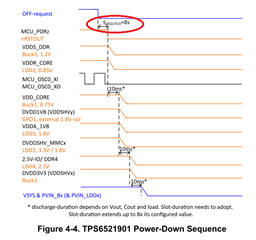

It depends on the NVM settings. The power-down sequence is gated by the slot duration and the rails being discharged below the SCG threshold. This means the power down sequence will complete after the duration for the last slot finishes and all the rails are below the SCG threshold. The technical reference manual (TRM) for each orderable shows the power-up and power-down sequence along with the duration. If you are using the TPS6521901 specifically, here is the link to the TRM: TPS6521901 Technical Reference Manual (See figure 2-1, 2-2)

If EN remains high, will it automatically enter the power-up sequence after completing the power-down sequence?

Do I have to turn off VSYS to reboot the PMIC?

If the enable pin goes from low to high while the PMIC is executing the power-down sequence, the device will automatically execute the power-up sequence again after the power-down is complete. Please refer to the TPS65219 online datasheet for a description of the COLD reset, I2C OFF request and Enable pin. These triggers can execute a power-down sequence but only COLD reset doesn't require a new ON-request.

Thanks,

Brenda

Hi Brenda,

Thank you, I understand.

I am using TPS6521901. I have one last question.

Is tDEGL_OFF 8 seconds?

The tDEGL_OFF value is not documented in the TRM.

Best Regards,

Hi,

The TRM only shows the NVM configurable register settings which are unique for each orderable. All the remaining parameters can be found in the datasheet. The OFF deglitch for the EN/PB/VSENSE pin (when configured as Enable) is shown in the capture below.

Thanks,

Brenda

Hi Brenda,

AN (slvafd0a) says 8 seconds, but is it different from this parameter?

Best Regards,

The function of the EN/PB/VSENSE pin is configurable. 8s is the OFF deglitch if the pin is configured as "push-button". If the pin is configured as "Enable", then the deglitch would be "tDEGL_EN_FALL".

Thanks,

Brenda