Hello

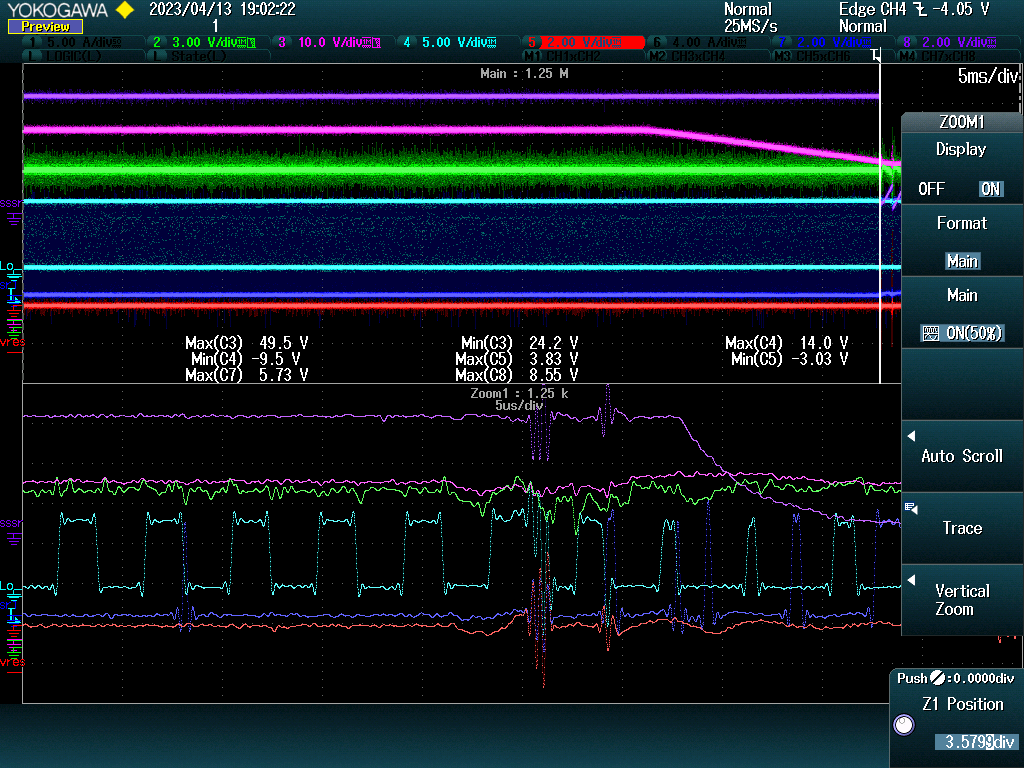

Our application is DC/DC converter, topology is half bridge and the input is 48V, we observed abnormal behavior during on/off test with LM5036, see below.

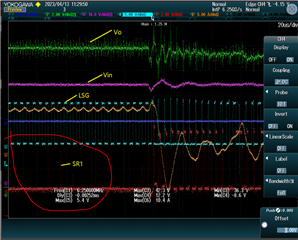

at normal conditions, the SR1 is complement to LSG.

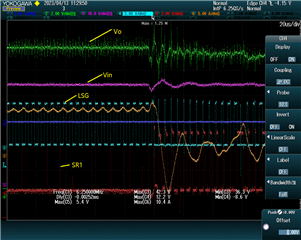

but sometimes we observe the SR1 is lost or operates at minimum duty.

from the datasheet, SR1 should either complement to LSG or synchronized to LSG. Can you let me know at which condition will cause the SR to enter into abnormal status?