Other Parts Discussed in Thread: TPS53832A

Hi, My Friend:

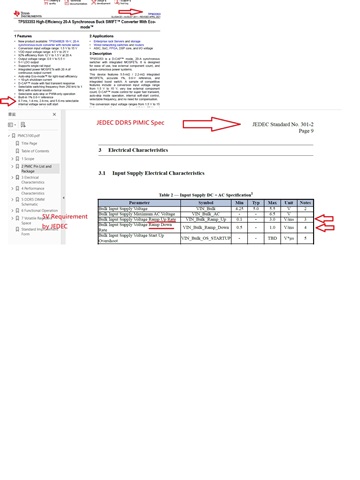

When studying JEDEC DDR5 PIMIC spec, I found Bulk Input (VIN-BULK, 5V) of DDR5 UDIMM/SODIM is restricted as below:

1) BULK Input Ramp UP = 0.1 ~ 3.0 V/mS

2) BULK Input Ramp Down = 0.5 ~ 1.0 V/mS

I also surveyed the datasheet of TI TPS53353, which was designed in Intel Raptor Lake-S Platform (RPV). My questions are:

1) Dose the soft-start mechanism of TPS53353 achieve "5VOUT Ramp UP = 0.1 ~ 3.0 V/mS?"

2) Is there any property of TPS53353 to achieve "5VOUT Ramp Down = 0.5 ~ 1.0 V/mS?" Which page of TPS53353 datasheet shows it?

I emphasize that TPS53353 is designed in Mother Board and to offer 5V to Bulk-VIN of UDIMM or SO-DIMM.

Many Thanks!

Sen