Team,

It looks like the VSYSPOR_Rising threshold is fixed at 2.2-2.5 V (see datasheet). So this would mean the PMIC starts it power up sequence after ~2.5 V are reached. But this would be too early for any internal buck which is configured for a 3.3 V output.

And the threshold is also too low to safely monitor any external 3.3 V or 5 V VSYS input.

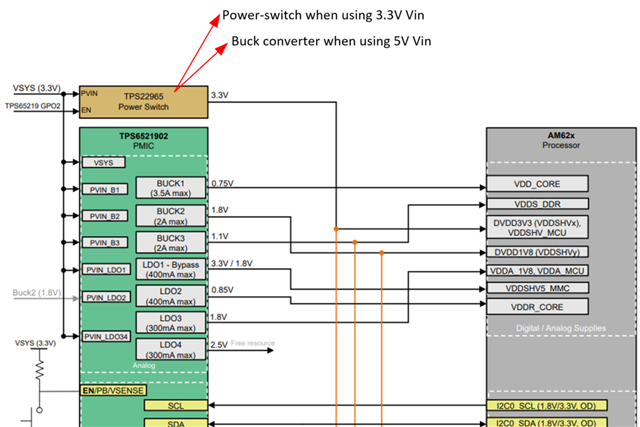

Therefore I would assume that in any case an external supervisor will be needed to monitor the VSYS input. This aspect is missing in application notes like “Powering the AM62x with the TPS65219 PMIC”.

Can you please clarify?

Thanks,

Robert