Hi,

I have a LM5146 based design. The design was done in TI Webench and initial evaluation was done with the LM5146-Q1-EVM12V.

The design inputs are very similar to the LM5146-Q1-EVM12V, however the output voltage is slightly higher at 12.5V and the output current is 25% greater at 10A.

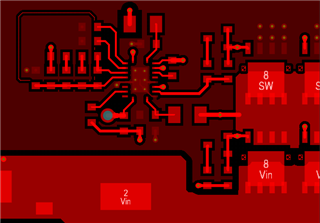

The layout closely follows the TI recommended layout in section 11.2 of the part datasheet.

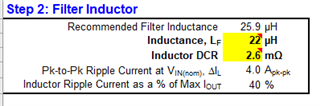

The key differences that Webench changed for the higher current were:

- Paralleling of two additional FET's

- Different inductor value and size

- All of the compensation network values

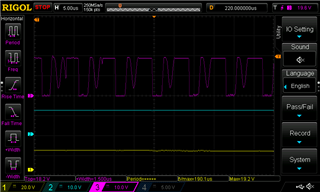

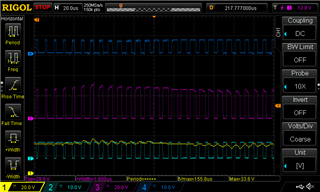

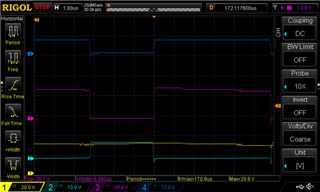

When I start to bring up the supply, with no load attached, the supply audibly "sings" and the input supply overcurrents and sags the input voltage. Connecting a scope to the switch node shows that the low side FET appears to be turning on with the high side FET on. Waveform and Webench design attached.

Magenta is switch node, Blue is output voltage (target is 12.5V), yellow is input voltage (initially 30V at 3A)

Thanks in advance for your support...