Hi everyone.

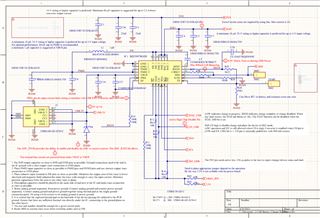

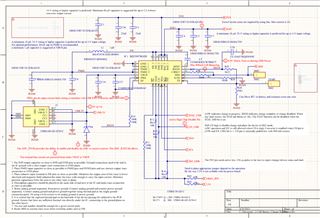

The BQ25887 IC is heating up while its charging on 1.2A from USB. The circuit is exact the same as the development board as shown below

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi everyone.

The BQ25887 IC is heating up while its charging on 1.2A from USB. The circuit is exact the same as the development board as shown below

Hello,

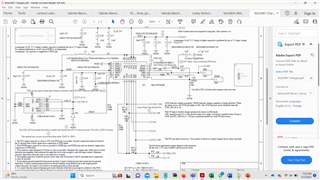

Can you please provide a schematic with the actual values for each part instead of the part number? For example, instead of GRM155R7E103KA01D have 0.01 uF 25 V? If you would like me to check the actual part number, please send those in a separate schematic. Also, please send a higher resolution schematic.

As for heating up, I need more details. This being an integrated part, the device will always heat up even if nominally as power is passed through it. What is the VBUS voltage, what is the battery voltage, what is the system voltage? Please provide more information.

Regards,

Mike Emanuel

Hi Mike,

Here im attaching a clear picture with capacitors and inductor value (drive.google.com/.../view. Furthermore I'm attaching second picture with all the measurement by using two different type of battery packs. As per my observation heating is happening with P2 pack.

| Battery Pack | VBUS | PMID | BAT | SNS | MID | I_usb | Heating |

| P2 | 4.58 | 4.51 | 7.08 | 7.11 | 3.17 | 1.45 | YES |

| P2 | 4.39 | 4.34 | 7.95 | 7.95 | 4.01 | 1.35 | Little |

| P2 | 4.65 | 4.63 | 6.93 | 6.94 | 3.4 | 572mA | YES |

| P1 | 4.26 | 4.2 | 7.33 | 7.34 | 3.64 | 1.243 | NO |

| P1 | 5.01 | 4.316 | 7.36 | 7.38 | 3.65 | 1.351 | NO |

Hello,

Three comments on the schematic.

1. We recommend on EVM 10 V rated capacitor for REGN, I see you have 6.3 V.

2. Also we recommend on EVM 25 V BTST capacitor.

3. Looking at your inductor, the DCR is almost two times what it is on the EVM. This will increase loss and could make the inductor hotter.

As for your results, I need more information. Can you please provide the full input/output parameters (ie input voltage/current and charge voltage/current)? Can you please provide more information besides "YES, Little, or NO" heating? Can you run the ADC and measure the Die Temperature? What is the individual cell temperature/voltage in each of these cases? Are the cells uneven voltage with P2 but not with P1?

What is the physical difference between P1 and P2? On P1 you can run higher 4.26 VBUS and 1.243 I_USB (5.3 W input power) but on P2 you run at 4.65VBUS with 572 mA I_USB (2.66W input power)? This does not make sense as P1 is running at a higher power level as P2 and the heating pattern is different (5.3 W input power P1 vs. 2.66 W input power P2). P1 has "NO" heating and P2 has "YES" heating for these use cases.

Also why is the last entry having 5.01 VBUS and 4.316 VPMID? That seems like a large drop for the input blocking FET.

Regards,

Mike Emanuel

Hello Mike,

Highly appreciate your suggestion and assistance. I'll replace the above two caps by the development board and let you know the results.

P1 is 2700mAh capacity 2 cell battery pack

P2 is Samsung INR18650-35E 3450mAh 2 cell battery pack with 2300mAh capacity

I_usb is the power drawing by the VBUS from the variable power supply which is indicated by the power supply. All the other voltage parameters were measure by the digital multi meter.

Best Regards

Salinda

Hi Salinda,

We need to answer several key questions. The capacitors are suggestions and are likely not the problem (though I encourage you to follow the recommendations).

We need to see how the charge current is in all of the scenarios. We can then see how the input power compares to the output power (for this we need input voltage/current and output voltage/current).

We need to see the actual die temperature reported in these scenarios. In fact, it might be helpful to turn on all channels of the ADC and report the findings.

We also need to know if the packs are unbalanced, meaning the top cell is higher voltage then the bottom cell.

Regards,

Mike Emanuel

Hello Mike,

I recently changed the capacitors, but unfortunately, I did not observe any change in the REGN voltage and BTST waveform. The bq25887 IC is still heating up as it did before the capacitor change.

To provide more information, I have included the following readings from the internal ADC IC register values:

V_BUS= 4.41V, I_BUS=2A , V_BAT= 7.35V, I_Charge_BAT= 1.088, Temperature = 55c after one minute and its reaching 80c after 5min

I also measured the following voltages using a DMM to confirm the values:

V_bus_dmm=4.37V, V_pmid= 4.314, V_sys=7.37V, V_bat_dmm= 7.31V, V_mid = 3.69V, I_bus_dmm = 2A

So the input power is 4.4 x 2 = 8.8W and output power is 7.35 x 1.088 = 8W. Seems like 0.8W power is dissipating by the bq25887 IC.

The data also confirm that two batteries are balanced.

It's worth noting that I am checking the performance of five boards simultaneously, and I'm getting almost identical observations across all of them.

Unfortunately, this issue has prevented us from delivering 30 units of Design Validation units. I urgently require assistance in rectifying this issue.

Best Regards

Salinda

Hi Salinda,

Did you follow the layout of the BQ25887EVM? I am running it right now with the following conditions from the ADC:

I have run the IC for more than 5 minutes not observing any nominal change in temperature. How is the IC heatsinked? According to Layout Guideline 6, "It is critical that the exposed thermal pad on the backside of the device package be soldered to the PCB ground. Ensure that there are sufficient thermal vias directly under the IC, connecting to the ground plane on the other layers."

Regards,

Mike Emanuel

HI Mike,

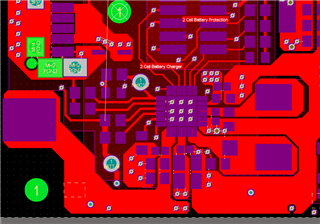

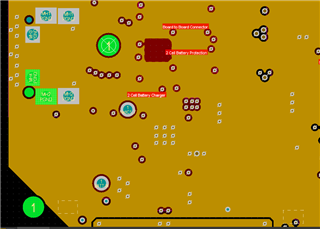

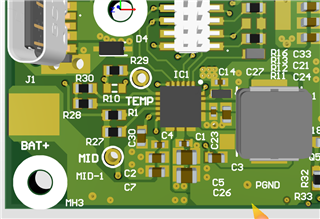

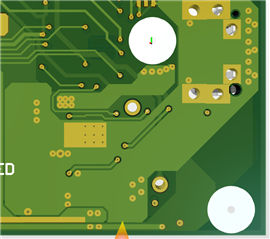

I follow all the layout guidance shown in the pictures below, ensuring that all traces are kept as short as possible and that the current density is minimized for higher power tracks. Additionally, I add nine thermal vias to expose the IC pad and facilitate a copper-exposed heatsink on the bottom side, which connects the Ground Plane and bottom copper pour of the four-layer board.

I greatly appreciate your help in running the IC and providing some comparisons. In my case, when comparing your results with mine, I am only able to achieve a charging current of 1A with a 2A bus current. This is where the problem lies.

TOP Side - Design View - Short Larger tracks with thermal vias

Inner GND PLANE

TOP Side - 3D View - Short Larger tracks

BOT Side - 3D View - copper-exposed heatsink and thermal vias

Best Regards

Salinda

Hi Salinda,

Can you please send me the full layout so I can evaluate it further?

What is the edge of the board temperature when this is occurring? I am wondering if your board is getting hot somewhere else and this is pushing the IC to get hotter because of proximity.

As for the charge current being only 1 A with 2 A input current, this is because this charger is a boost converter. Let us just estimate from 5 VBUS efficiency in datasheet with 7.6 V battery and 1 A charge current. The efficiency is about 92.3%. Your output power is 7.35 V x 1.088 A = 8.00 W. Divide by efficiency, input power should be around 8.66 W. Your input power is 4.41 V x 2 A or 8.82 W. Please note the 92.3% efficiency is not spot on as it is an estimate for illustrating this purpose. The close alignment of the power shows that with a boost converter with the parameters specified you will get 1 A charge current for 2 A input current. Boost converters step up voltage and step down current.

Regards,

Mike Emanuel

Hi Mike,

Attached is the layout file that we discussed. Could you please review the full layout when you have a chance? I wanted to mention that there are no heating components nearby, yet the I2C die appears to be heating up to 80C. I will send you the FLIR hotspot image as soon as possible to help us better understand the issue.

BR

Salinda

Hi Salinda,

We do not use google drive for our work purposes. If you can post the files here that would be helpful.

Regards,

Mike Emanuel

Hi Mike,

Please find the attached layout file and highly appreciate if you can review it.

BR

Salinda

Hi Salinda,

A couple of things stand out:

1. There is no analog ground. Please adhere to Layout Guideline 5.

2. This is probably the most important. I do not feel as if there are enough thermal relief vias on this design. There are 4 spaced out vias for BAT, and long lengths of copper for PGND that do not have any thermal vias. Two of the thermal vias for BAT are on a displaced current path. On top of that, the PGND pour next to the chip isn't connected to the thermal pad on the top layer. Please follow Layout Guideline 6.

3. It may not have an impact, but the REGN pin current is being pulled to the TS circuit before it connects the REGN capacitor. It is close enough it may not matter, but in general it is good practice to place the bypass capacitor as close as possible to its pin and draw current after that.

Regards,

Mike Emanuel

Hi Mike,

Following modification done to the PCB

1) GND Bonding improved with more vias and copper pours on all four layers

2) Cooling improved by adding more thermal via's

3) Separate analog via accommodated in third power layer. (Note : need to connect it to the 9 Thermal vias during Gerber generation)

Please find the attached modified layout file and highly appreciate if you can review it.

BR

Salinda

Hi Salinda,

1. Ground vias are more numerous.

2. Looks like there are significant more vias, this should help with the heat.

3. Looks like analog ground has been added. Please connect ILIM through analog ground like in BQ25887 EVM User Guide. Good job on connecting GND pin to thermal pad.

Regards,

Mike Emanuel