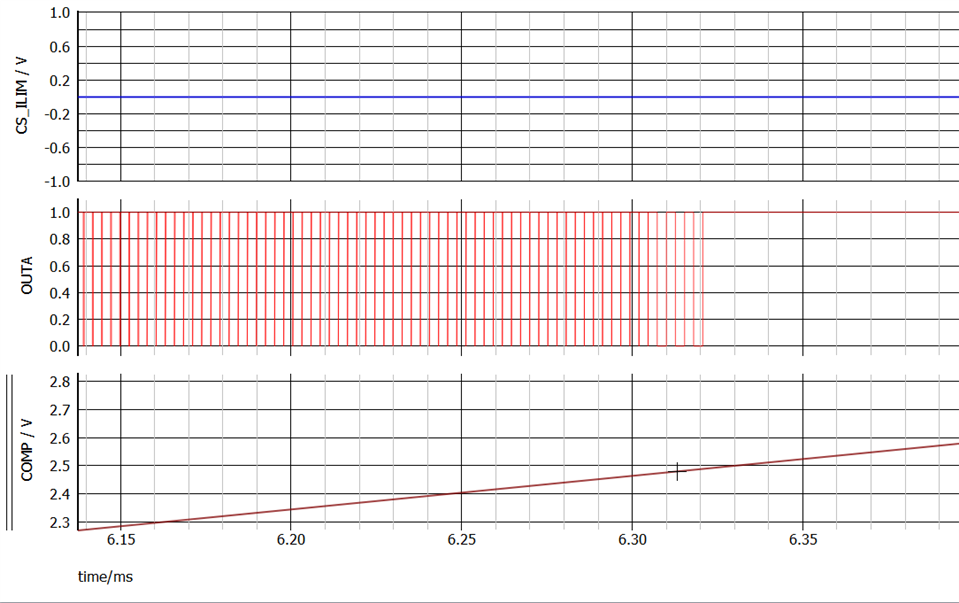

I'm seeing some strange behavior from the SIMPLIS model when I sweep the COMP voltage over the full range (for example, applying a slow low-amplitude ~150Hz triangle wave voltage across VSENSE about its nominal center point, and loading COMP only with a resistor to convert current to voltage + a 1pF capacitor to set initial conditions). What happens is that as the COMP voltage slowly rises up above the saturation point of about 2V, the PWM outputs (OUTA, SRA, etc.) suddenly glitch their duty cycle from near-max (which would be expected with COMP at this high voltage) to (max-50%). So when DCL is grounded setting max D to 50%, the output OUTA glitches to the minimum ON time (despite COMP continuing to increase slowly above 2V) and continues to do this across several switching cycles until COMP reaches a slightly higher amplitude (2V + some fraction of a V, exact amount depends on switching freq for some reason). If I pull up DCL increasing the max duty cycle to 100%, the output OUTA glitches down to 50%. The exact COMP voltage points where this glitch starts and ends varies somewhat with switching frequency, as does the length of the glitch pulse, but in general a doubling of the switching frequency doubles the time duration of the glitch.

I've been over the datasheet several times and haven't found any reference to this behavior being expected for the device, so wanted to reach out to see if this is indeed expected, or if this should be taken to be an error in the model.

Supporting screenshots:

PWM connections (no loads on OUTA or SRA)

Slow triangle modulation of PWM_SENSE input

SIMPLIS sim results (Fsync=750kHz, DCL grounded --> Dmax 50%) showing first a zoomed out view of the main PWM voltage waveforms, which at this zoomed out view seem to be behaving just fine, but then below I zoom into one of the glitch regions about 2/3 of the way through the sim when the triangle modulation of the COMP pin creeps above 2V, then reverses and drops below again. I've circled the 2 regions in this bottom plot where an unexpected glitch of OUTA (and SRA if you look closely) occurs.