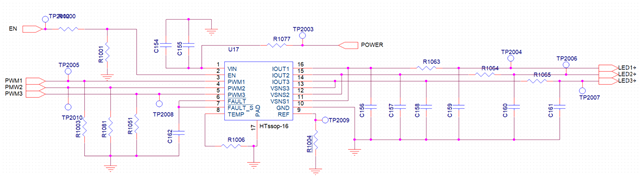

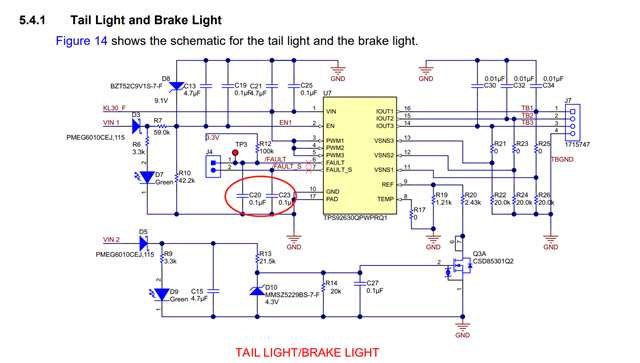

when i use the TPS92630 IC, three channel apply ,refer to the following circuit:

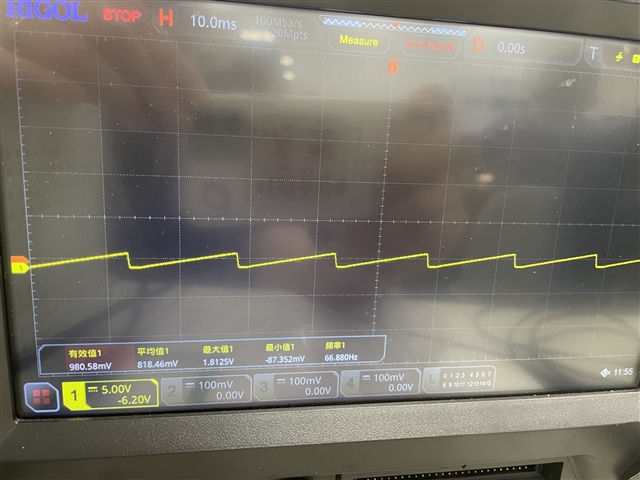

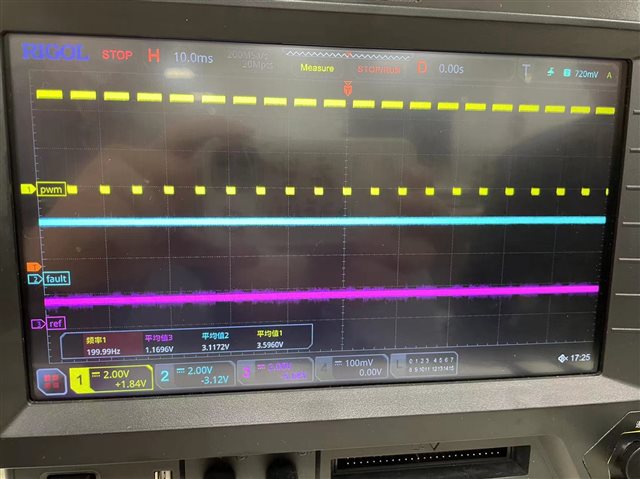

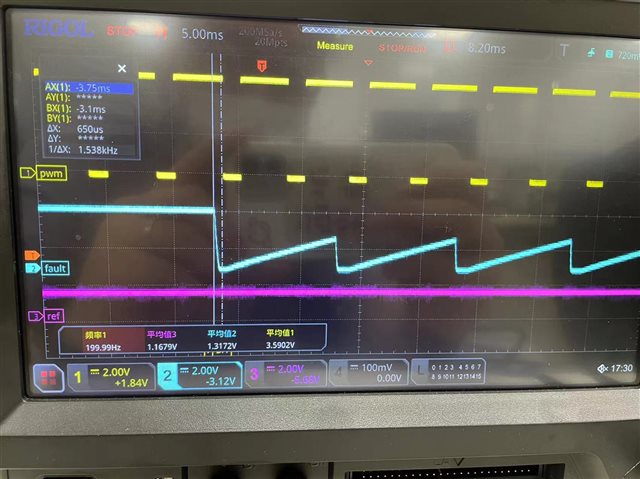

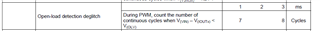

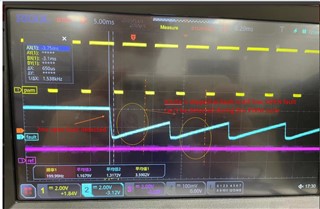

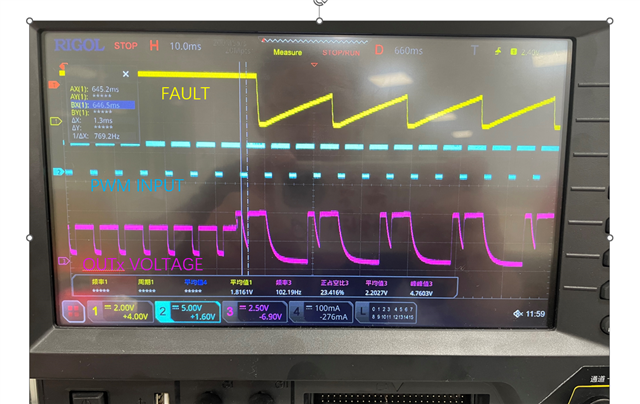

PWM signal generated by MCU, IC driven three way LED, But when I disconnected one channel LED, the remaining two channel LEDs began to flash,

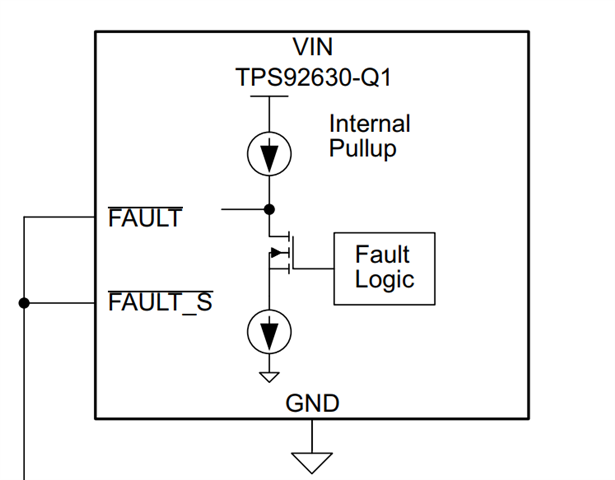

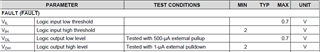

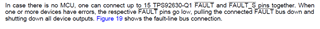

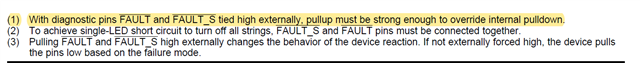

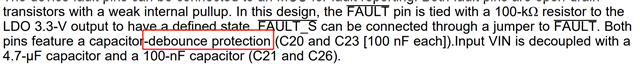

Why is this happening?During this period, PWM1,2,3 has been continuously inputted , i think I connect pins 6 and 7 together, when one LED goes out, the other two LEDs should go out together,

Why do I disconnect one channel LED and the other two channel LEDs flash instead of going out ? could you explain it to me ?

thank you~