Hi,

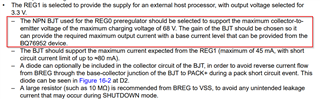

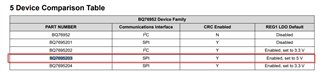

I am using BQ7659203 SPI comm support devices and facing following issue

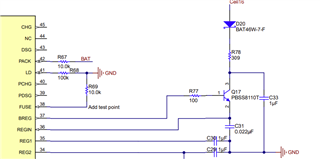

(1) applying 5.0V at REGIN pin and not using any LDO FUNCTION of this device and not using any TS!/TS2 pin, whenever i am plugging cell connector before giving +5V externally ,its damaged means

its VREF 1.8 V o/p is not build .

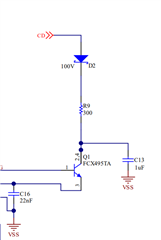

(2) if i am using this suggested supply ,output at VREGIN is approximate 6.0 V ,Is OK or require to reduce this , transistor is MMBT5551

Please suggest ...it is urgent .