Other Parts Discussed in Thread: BQ25790, ,

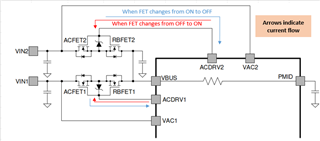

1) Is it possible to change the value of IINDPM by changing the resistance of the ILIM_HIZ pin during charging and input power switching?

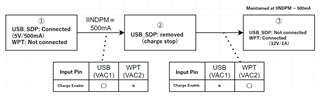

As background, we want to set IINDPM separately by hard switching because different voltages are input to VAC1 and VAC2 even when the SOC module is not activated.

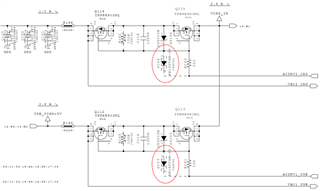

Please give me your opinion if it is possible to hard-switch IINDPM from two different input sources in the circuit shown in the red box below.

(I am assuming that if both inputs are present, IINDPM is to be set software).

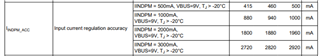

2) If two different power supplies are used for input power and operated with a single input current limit, IINDPM is recommended to match which of the following conditions?

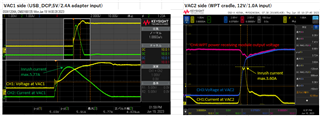

VAC1: USB connection, 5V/2.4A

VAC2: WPT power supply, 12V/1A

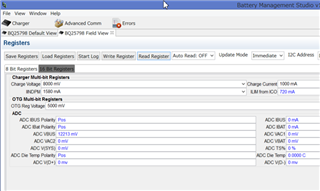

Note that it is assumed that the ICO function is enabled during charging.

3) Is it correct that IINDPM is automatically adjusted to prevent the adapter from overloading even if the load status changes midway after the ICO function is enabled (EN_ICO = 1, ICO_STAT_1:0 = 2h)?

If EN_ICO=1 is not enough for automatic adjustment, please let us know when to set FORCE_ICO =1 to prevent excessive current draw during load changes.

Regards,

Kagawa