Other Parts Discussed in Thread: UCD9090

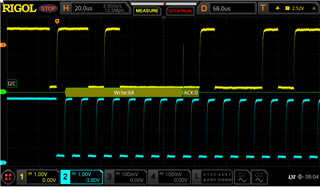

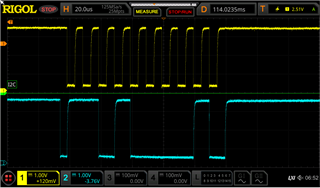

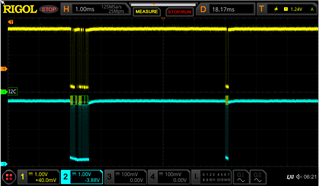

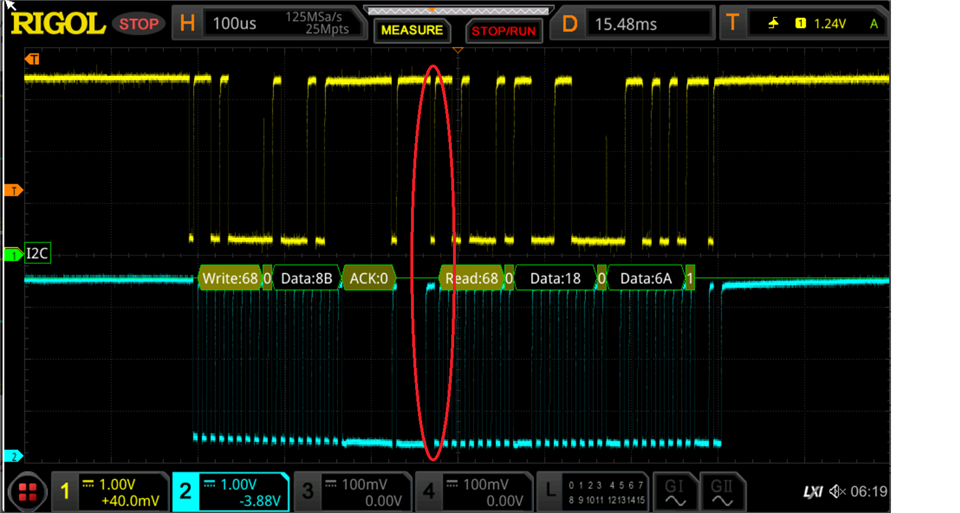

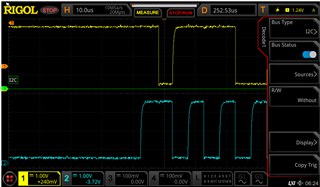

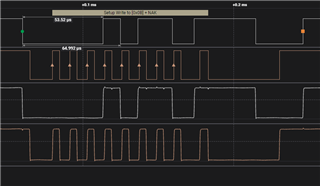

Using our I2C adapter inside our Xilinx FPGA XIIC to communicate to the UCD9090A over the PMBus, and using a Salae logic analyser to capture the waveform below, we are reading command 0x8B, the device address is 0x68. Every so often, like 5% of the time the device is not ACKing its address. From this snapshot, it looks like a valid I2C transaction with a NAK instead of an ACK from the UCD9090. Any idea why this would be happening?