Hi,

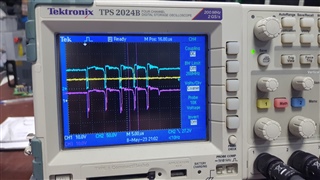

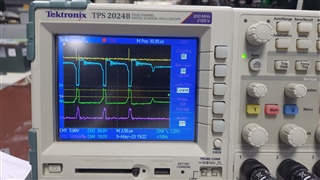

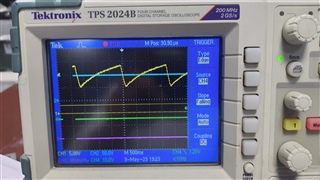

I am designing an isolated DC-DC converter using UCC28780. It has some startup problems. The converter is restarting after 6 switching cycles (ULVO cycle reset). Observed that No overcurrent, Overtemperature, brownout,CS pin open/short, HVG overvoltage, thermal shutdown, RDM pin open/short, RTZ open/short No output overvoltage protection are triggered. Please let me know what could be the problem. I would appreciate if you could analyze the problem and give a solution

Please also find attached the calculation sheet.

CH1: Vdd, CH2: Low side GaN Vds, CH3: voltage across auxiliary winding

CH1: Vdd, CH2: Low side GaN Vds, CH3: voltage across current sense resistor, Ch4: voltage across secondary winding(scope probe is connected secondary ground)

UVLO cycle