Hi Team,

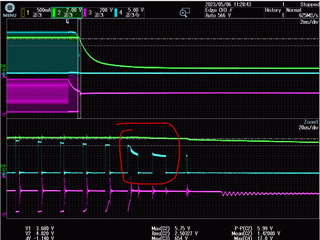

Customer feedback that when short output of UCC28C44, the device will have an abnormal behavior on PWM pulse, which is shown below:

Where CH2: VCC, CH3: Vds, CH4: driver pin

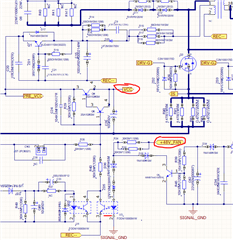

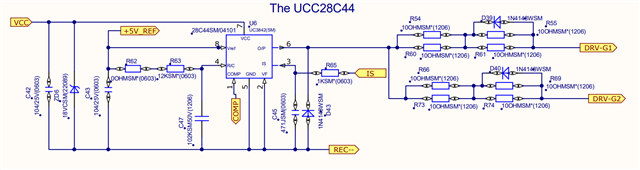

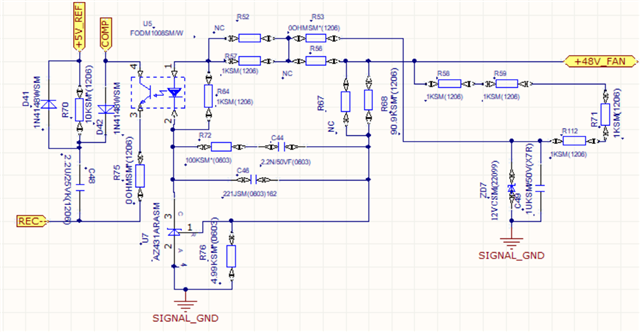

And the schematic is also attached below:

Thanks in advance.

BRs,

Francis