Hi Team,

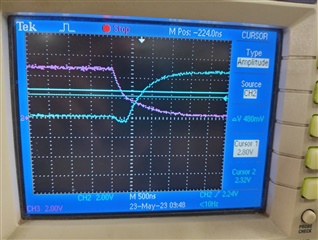

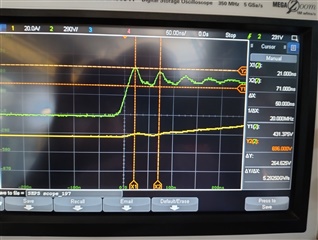

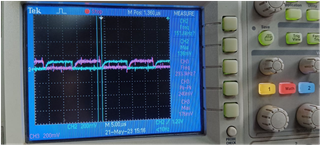

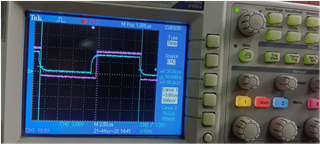

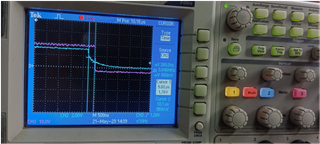

I am using UCC21710-Q1 driver IC for SiC MOSFET (C3M0040120D). 50kHz signal is generated with 160ns dead time using DSP board. The output from the DSP card is given below with 160ns dead-time.

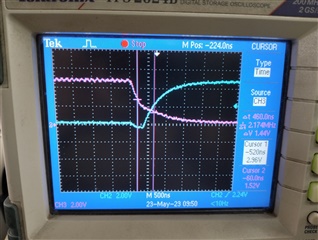

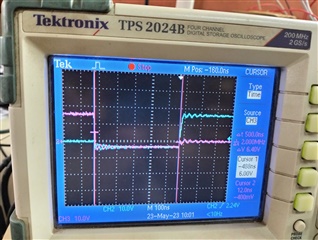

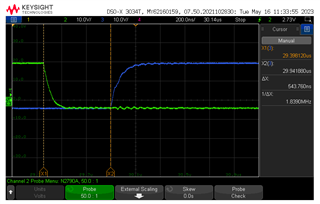

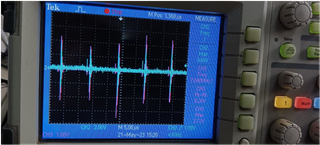

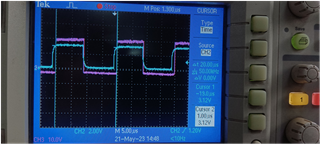

Same signal is given to input to the Driver board through FRC cable and the output of the driver is given below

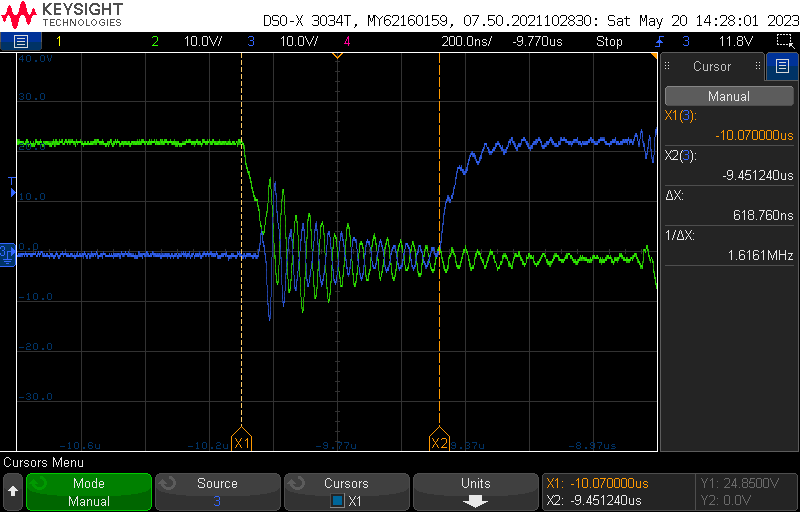

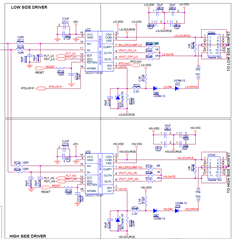

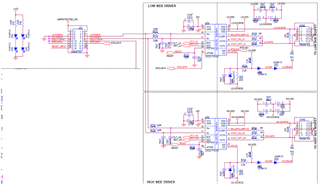

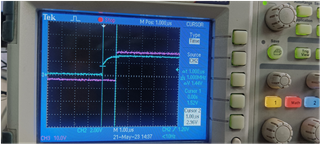

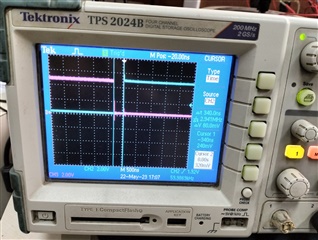

I have observed that there is Dead-time difference of 350ns. Can you please suggest, why this extra dead-time is adding to gate pulses. I have added RC (R=120R and C=56pF) filter at the input of the driver IC as per the datasheet. The driver circuit is given below for your reference

Thanks in advance for your inputs.

Regards

Umamaheswararao

Input pulses with dead-time 340ns

Input pulses with dead-time 340ns OUTPUT pulses with dead-time 440ns

OUTPUT pulses with dead-time 440ns