Hi,

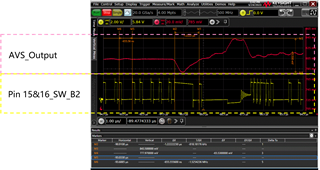

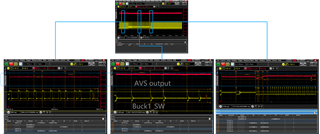

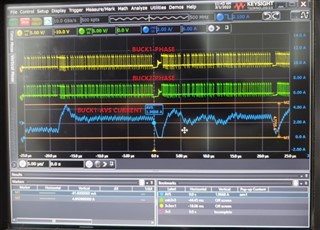

We used 1212 and 1111 power solution for TDA4 soc. The AVS output of 1212 is PFM mode after boot successfully.

Now we wanted to change AVS to PWM mode, and rewrote bit1/bit2 in 0x04 (in 1212) in SBL stage.

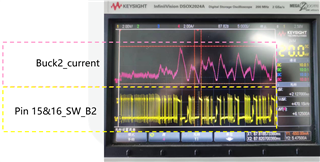

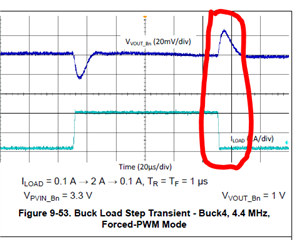

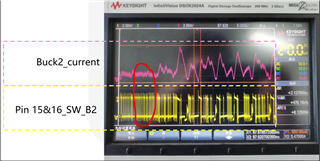

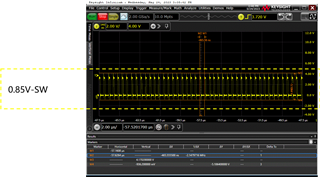

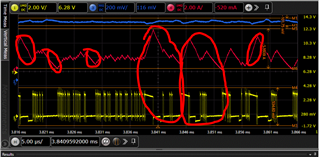

After tested, we found that that register is right, but the waveform isn't correct.

we read the register by the iic tooling.

The AVS operation is still held in PFW mode.

So, my question is including,

- we rewrote the bit before SOC fully running. and SBL stage is right?

-

Is there other operation before and after writing, only the bit2 in 0x04 is ok?