Hi Experts

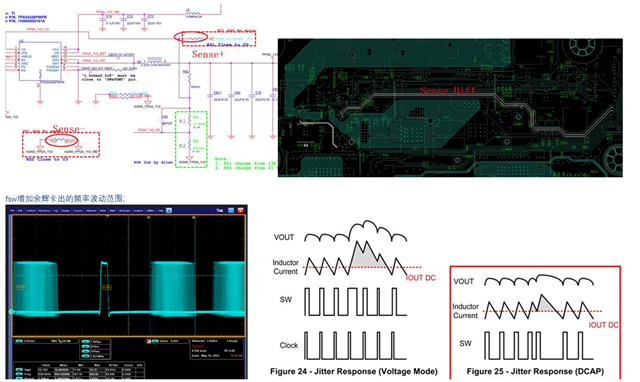

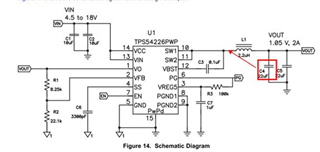

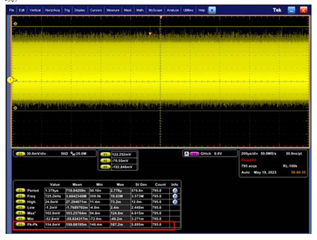

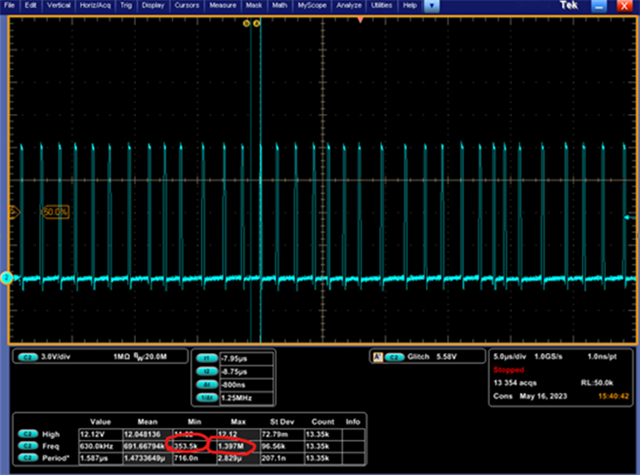

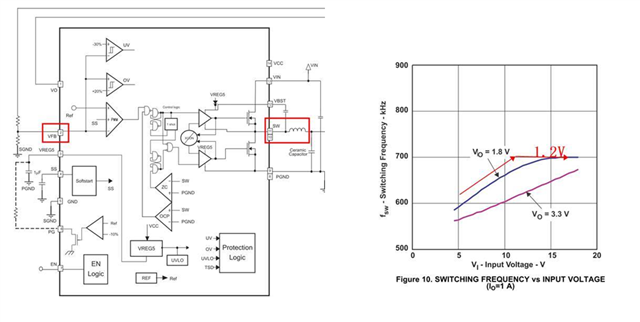

our customer find switching frequency have jitter. datasheet is 700kHz but when they use long time .

frequency maximum value would be 1.397Mhz and minimum is 353.3kHz.

customer have four question want to check with you

1. switching frequency range.

2. which reason will influence jitter.

3. if the range of jitter is too large . would it influence IC life cycle?

4.if VFB pin is disturbed , would it influence SW pin?

best

regards

brian