Other Parts Discussed in Thread: TIDA-010208

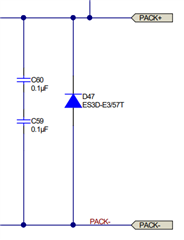

The customer used 6000uf in the PACK+ and PACK-.

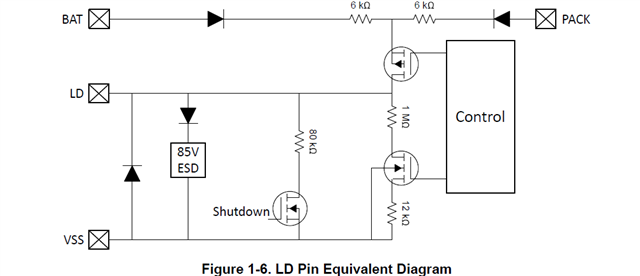

When the customer want to enter shutdown mode, it will last too much time until the LD pin voltage decreased to VWAKEONLD.

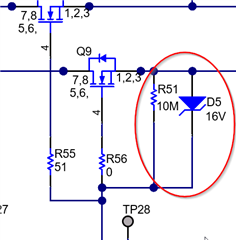

So in the LD pin, the customer want to use larger resistor like 1M instead of 10k, and then the detected voltage level will be below VWAKEONLD.

Besides, Set "protections load detect:active time" to 0 for the normal operation of OCD latch and SCD latch.

If the customer choose this design, is there any other risk not in the consideration?

Thanks