Hi,

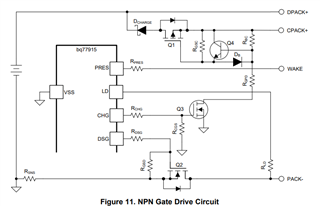

In the image below, I examine the high side switching method with the bq77915. I couldn't quite understand the PMOS structure on the CHG side. I tried to simulate with LT spice and couldn't control PMOS.

I am using the values given in the application note in the LTSpice image. Normally I connect V1 source and drive Q3 mosfet to simulate Chg voltage. Regardless of the state of Q3, Pmos(q1) is always ON, even if the mosfet of Q3 is off.

I would expect Q1 to be off when Q3 is off.

There is an issue on my mind.

Im worried that under error conditions, pmos won't turn off.

In the BQ77915 datasheet, there is a table showing which mosfet (DSG-CHG) is on/off under various fault conditions. For example; In OV, CTRC, OTC, UTC error conditions, the CHG mosfet (high side pmos) must be turned off.

Thank you

.