Other Parts Discussed in Thread: TUSB544

TUSB544 demo setting:

I2C_EN: F

SLP_S0#: 1

SWAP:0

- TUSB544 EVM demo 2 lane DP+USB3.0 function, upstream connect PC, downstream connect type C hub ( which support HDMI and USB3.0 function), we found USB3.0 function is OK, but 2 lane DP function only can work normally on type C one side, other side can’t display normally in 2 lane mode ,checked flip pin have status change accordingly.

- 4 lane DP mode, demo bard R1/R2 are populated, so AUXP connect directly to SBU1, AUXN to SBU2, but why does the function can work normally when flip type C?

- For TUSB544 source side and sink side setting, what’s the difference for function or performance? We tested no difference.

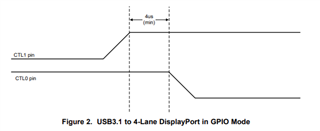

- From USB3.1 mode to 4 lane DP mode, does any timing of CTL0 and CTL1 required? Demo board default setting is CTL0=H, CTL1=L and USB3.0 mode without no timing, but why can this setting change to 4 lane DP mode successfully?