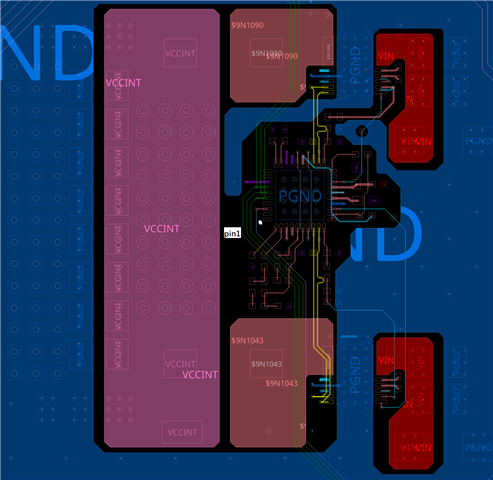

Hi TI Team,

I have some re-spin PCBs return but I found the chip performance is not very stable now.

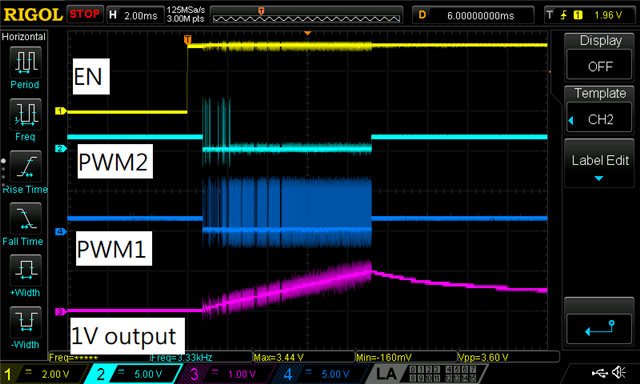

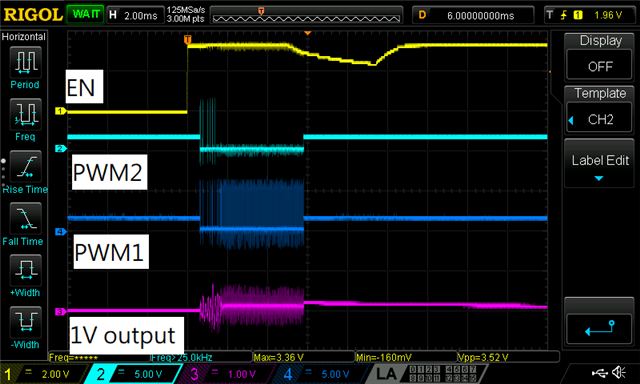

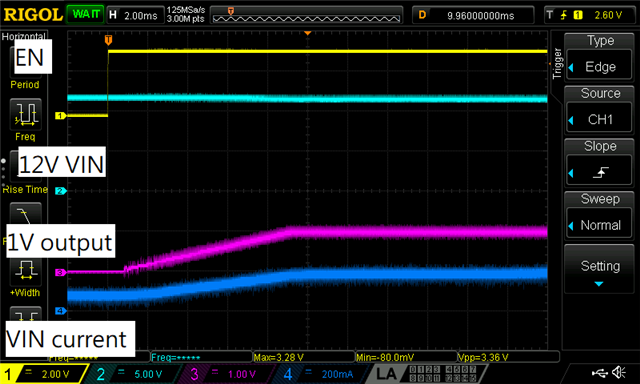

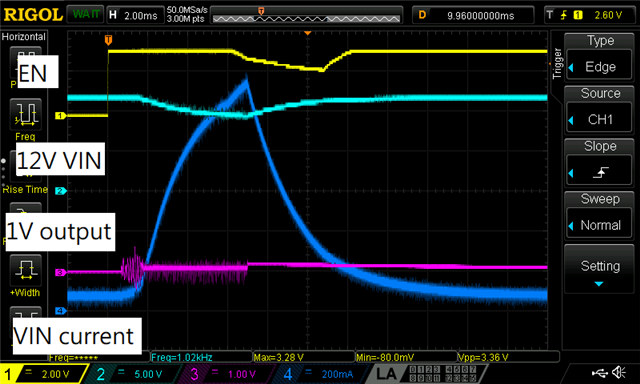

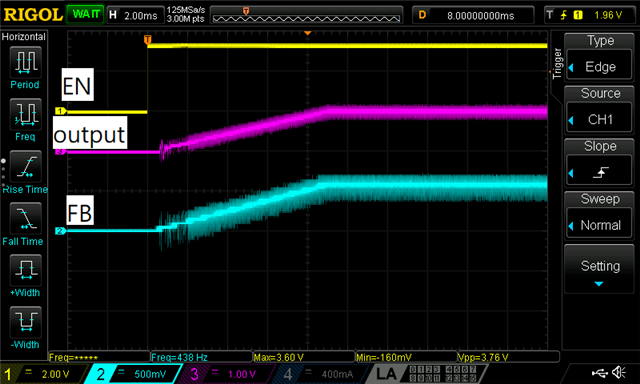

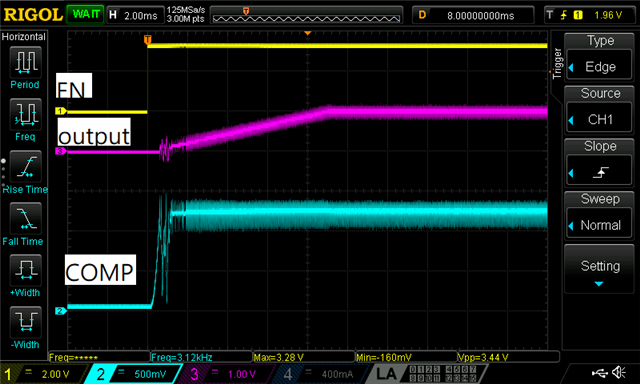

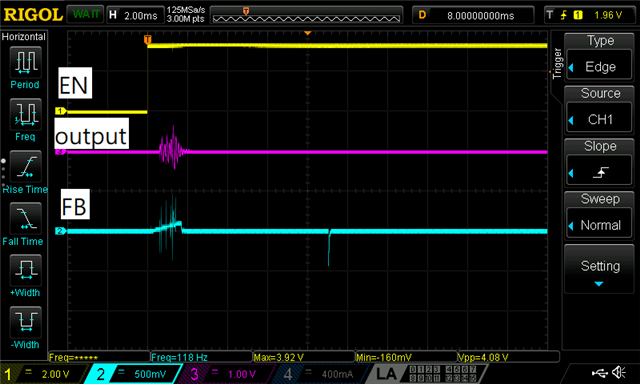

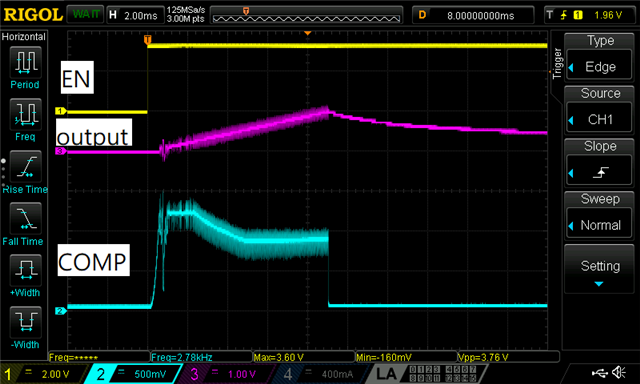

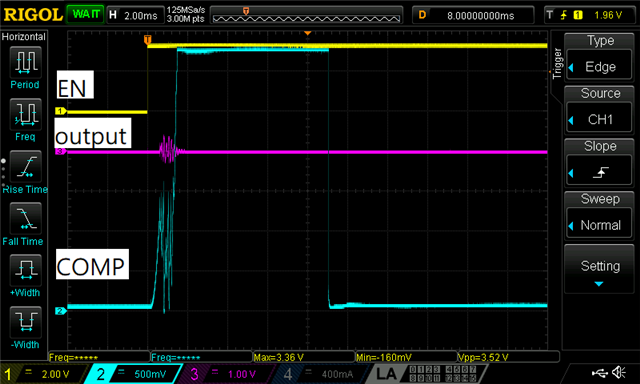

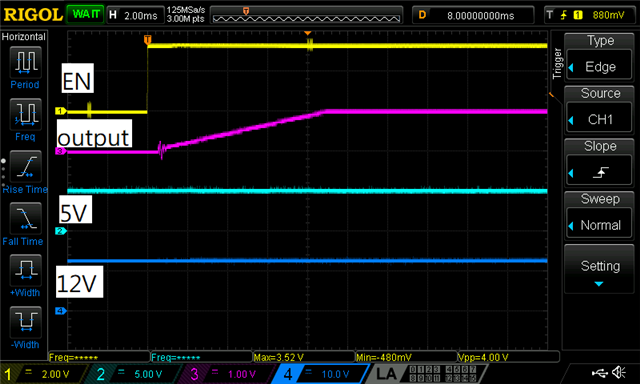

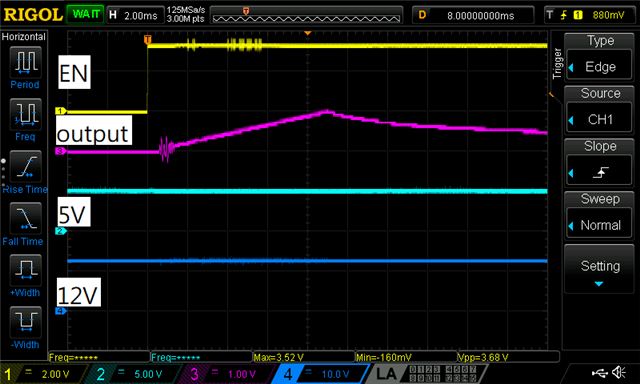

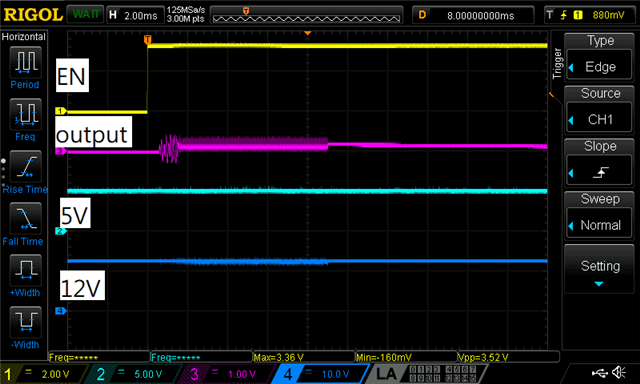

When I apply the enable signal to TPS40428+CSD95378B, the system cannot provide 1V output in 1 go.

As I see it usually cause large current in the first time (12V input drop to 9V) and undergo a few restart before output stay on 1V.

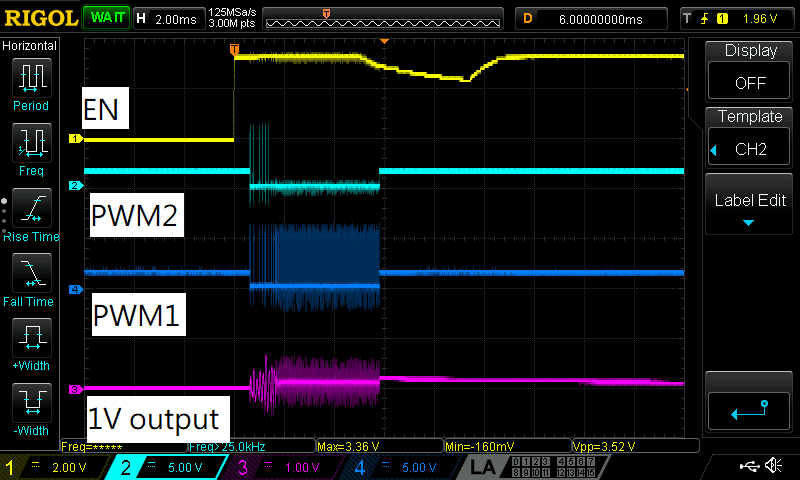

Tracing back I found 1 of the PWM signal stay idle when powering up...

Can we get any hints from below waveform?