Hello,

The mosfet is broken in the jumpstart test, how can we solve this problem?

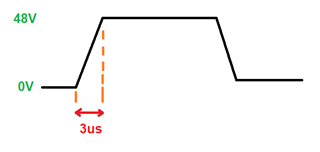

In the jumpstart test, the voltage goes from 0V to 48V in 3us and stays there for 1 minute. As a result of the test, the mosfet (Q1) remains as a short circuit, and after a while the OVP is broken.

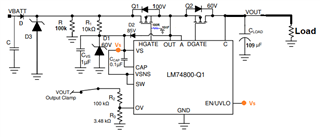

I created a similar schematic of the product I designed, below.

What should we do both to pass this test and to pass the 7637-2 pulse tests that we will enter in the future, thank you in advance for your support.