Other Parts Discussed in Thread: AWR1642, TPS7A52-Q1,

Hi BU team

My customer used LP87702D-Q1+TPS7A52-Q1 to provide the power rails to AWR1642. AWR1642 would be latched off in bootloader stpe after write SW_reset bit to LP87702D-Q1 via I2C interface. Customer has below concerns to be get clarified. Customer doubted if re-startup sequencing after SW_reset configuration didn't meet the AWR1642 requirement?

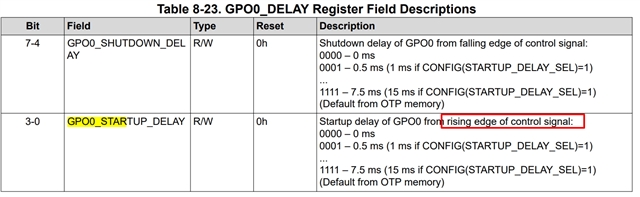

1. In the description of GPO0_startup_delay in 0xC register, what's the control signal? EN1?

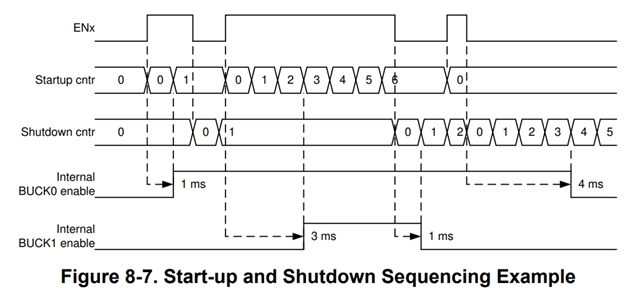

2. Does LP87702-Q1 share the same startup behaviors for the first startup and the re-startup after the configuration SW_reset bit? Does EN1 be toggled after the configuration SW_reset bit?

Would help share the re-startup sequencing example like the diagram in Figure 8-7 of datasheet?

Thanks