Hi TI Team,

We designed bms with bq76952 and we already used this bms under these conditions:

100A continuous discharge with 14 parallel fet(7 charge and 7 discharge, these mosfets specs are; gate charge 210nc @ 10v and Vgs 4.5V @ 250µA )

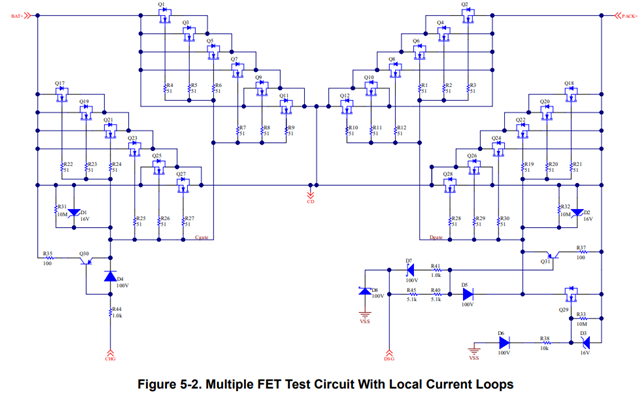

If we talk about on TI Multiple FETs with the BQ769x2 Battery Monitors Application Note, our gate resistors(r4,r5,r6..-r1,r2,r3..) is same with this application notes value 51 ohm and also our R44 is 1k to our R45+R40 total resistance is 57k and R41 is 1K this circuit works fine under 200A discharge(10s-15s),

However, when we use 16 parallel fet(8 charge and 8 discharge, these mosfets specs are; gate charge 210nc @ 10v and Vgs 3.8V @ 270µA ) but in this situation we can't open fets over 120A discharge current and I2C communication fail at this time.

if we start the load with 100A and increase the current to 150 or 200A while the load turn on, FET was still open but when we start the load with over 120A, FET was turn off.

We tried these solutions;

First, we think problem will occur because of the CP1 capacitance then we increase both the CP1 and BAT capacitance 1uf and try it. We repeat the same steps until both capacitances reached 18uf but nothing changed

Second, we increase R45+R40 and R1 the decrease these resistors values different level but nothing change

Third, we remove the D7. The closing problem doesn't happen so we turn-off the FETs over R45+R40(56K) and this mean our turn-off time get long, this create two different problems. First problem is turn-off time too long for SCD protection and second problem is mosfet drived at linear region to long and fets crush at scd.

Fourth, we decrease R45+R40 1K ohm while D7 is removed. It still can't turn-on until R45+R40 total resistance increase to 33k but the result almost the same as the third step.

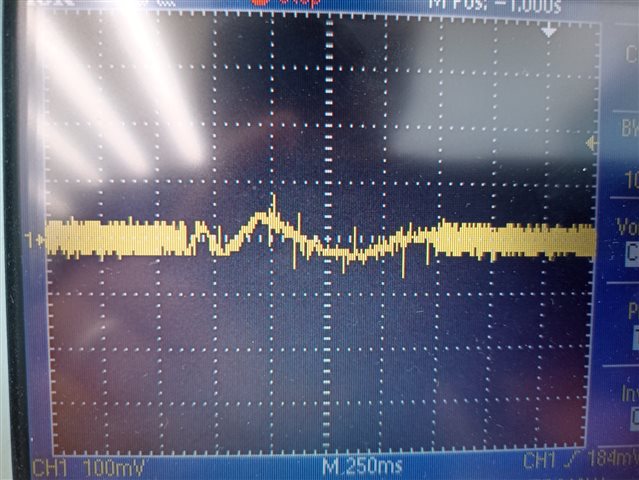

This picture shows the voltage on the shunt resistor when trying 150A discharge but fet problem occurs in that instance.

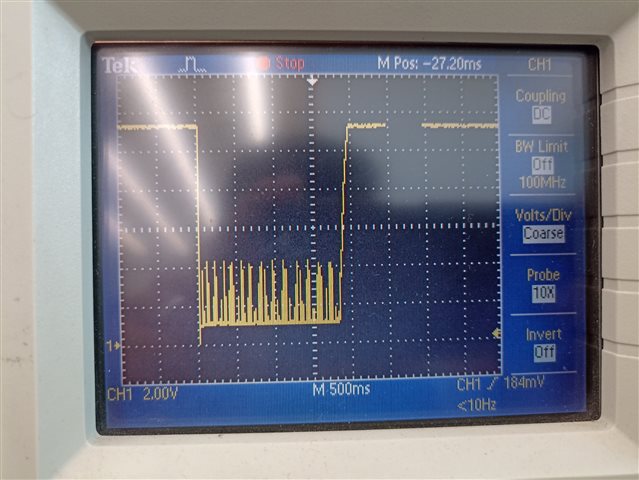

The second picture shows the Vgs voltage of the fets when trying 150A discharge but the fet problem occurs in that instance.

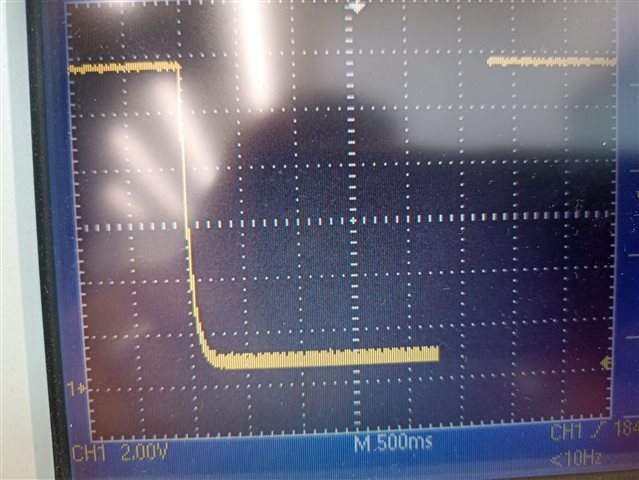

thirth picture shows CP1 voltage during same stiuation

Thanks in advance,

Canberk