Hi,

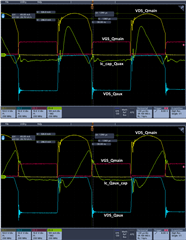

We are optimizing our low side active clamp forward converter with synchronous rectifier and the following figure shows the VDS_Qmain (Ch1), VGS_Qaux (Ch2), VGS_Qmain (Ch3) and the current from clamp capacitor to Qaux (Ch4). I tried different delay durations but there is a strange constant current flowing from Qaux to Cclamp when VDS_Qmain = 0 V. Is there any reason specific for this topology?

Cclamp = 20 nF and Fsw = 250 KHz.