Hi,

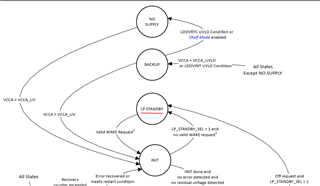

The datasheet illustrates the device power state by the diagram below. Only LP_STANDBY is mentioned, I wonder what about STANDBY when LP_STANDBY_SEL = 0?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

The datasheet illustrates the device power state by the diagram below. Only LP_STANDBY is mentioned, I wonder what about STANDBY when LP_STANDBY_SEL = 0?

Hi Zehui,

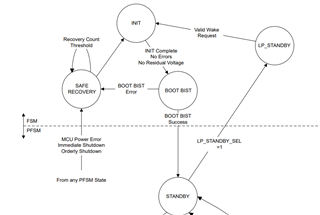

The STANDBY state is one of the pre-configurable mission states of the device, and is included in the Mission States bubble further down in the diagram you have provided. The specifics of the mission states will vary with the NVM of the device. The user guide for your device will show these transitions in the pre-configurable finite state machine (PFSM) mission states and transitions figure.

For example, the user guide for TPS6594133A has the following state machine diagram, with the STANDBY state included in the PFSM:

LP_STANDBY is part of the fixed device power portion of the FSM and will not be changed between devices. This is why we are able to describe LP_STANDBY in the diagram in the datasheet for all variants of the device.

Regards,

Megan

Megan,

Thanks.

Q:1. In the diagram you post there is not a direct transfor from INIT to LP_STANDBY. What will happen when VCCA is valid with no valid WAKE request?

2.When LP_STANDBY_SEL = 0, will INIT always be executed to BOOT BIST, whether WAKE reques is valid or not?

3.Is BOOT BIST success always followed by STANDBY?

Hi Zehui,

No problem!

1. When VCCA is valid with no WAKE request with the NVM described by the state diagram I provided, the device will stay in the STANDBY state. Even if LP_STANDBY_SEL is set to 1, the device will stay in the STANDBY state until the valid WAKE request is received.

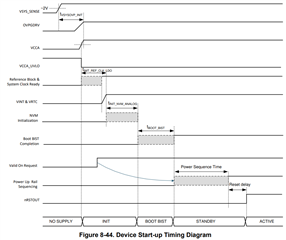

2. Yes, INIT will be followed by BOOT BIST regardless of a valid WAKE request. The Device Start-up Timing Diagram from the datasheet shows the valid ON request is only taken into consideration once the BOOT BIST has completed.

3. Yes, BOOT BIST will be followed by STANDBY until the valid WAKE request is received. This is also shown in the Device Start-up Timing Diagram before the device transitions to the ACTIVE state.

Regards,

Megan

Megan,

Thanks for answering. I still have some questions.

1. "When VCCA is valid with no WAKE request with the NVM described by the state diagram I provided, the device will stay in the STANDBY state. Even if LP_STANDBY_SEL is set to 1, the device will stay in the STANDBY state until the valid WAKE request is received."

Why will the device stay in the STANDBY state when STANDBYLP_STANDBY_SEL =1? There is a direct transfor from STANDBY to LP_STANDBY when STANDBYLP_STANDBY_SEL =1 in the diagram you provided.

2. "Yes, INIT will be followed by BOOT BIST regardless of a valid WAKE request. The Device Start-up Timing Diagram from the datasheet shows the valid ON request is only taken into consideration once the BOOT BIST has completed."

In the diagram I provided in the beganning, there is a direct transfor from INIT to LP_STANDBY. It seems the device never reach BOOT BIST in this situation.

Hi Zehui,

I will check with my colleagues on the specifics of what happens when the device is initially powered on and the transition from the INIT state to the LP_STANDBY state.

Experimentally, I was able to find the device stayed in the STANDBY state before the first WAKE event, even when LP_STANDBY_SEL = 1. I used the TPS65941515 NVM, which has the same connections between INIT, BOOT_BIST, STANDBY, and LP_STANDBY as I have shown in the previous diagram.

When the device was turned on with ENABLE pulled low, the device stayed in the STANDBY state with the BUCK and LDO outputs all at 0V. I measured a non-zero voltage out of LDOVINT, which meant the device was not in LP_STANDBY. I was able to write to LP_STANDBY_SEL before ENABLE was pulled high, but LDOVINT did not fall to 0V. Once I enabled the device at least once, the device transitioned to the LP_STANDBY state as expected.

According to the NVM configuration file, the device enters the mission states through the PFSM_START state and the WAIT4ENABLE state. The PFSM_START state configures the triggers, and the WAIT4ENABLE state ensures all the outputs are off while waiting for a WAKE request. This state functions the same as the STANDBY state since all of the outputs are powered off. Since I was writing the LP_STANDBY_SEL value during the WAIT4ENABLE state, that may have been why I could not experimentally start the device in the low power standby state. I will check with my colleagues to make sure. The PFSM_START state and WAIT4ENABLE are mainly referenced in the Scalable PMIC's GUI User’s Guide (Rev. B).

Regards,

Megan

Megan,

Thanks for sharing you experiment. I'm looking forward to your further reply.

Hi Zehui,

My colleague agreed that my initial experiment did not transition to LP_STANDBY due to the device being in the WAIT4ENABLE state. He mentioned retrying the experiment with LP_STANDBY_SEL configured in the NVM, rather than the I2C write I had previously tried. This would configure the bit before the device reached the PFSM_START and WAIT4ENABLE states. Once this change was made in the NVM, the device still turned on with LDOVINT high, indicating the device was in the WAIT4ENABLE state, not the LP_STANDBY state. After enabling the device, the device could then transition to LP_STANDBY when ENABLE fell. This was the same result found when LP_STANDBY was set to 0 in the earlier experiment.

Because we are not reaching the LP_STANDBY state, we are always going through the BOOT BIST after the INIT state.

We are looking into redrawing the diagrams to make this transition clearer.

Regards,

Megan