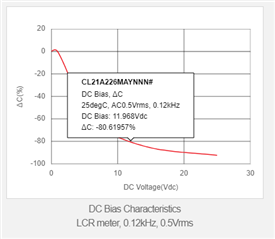

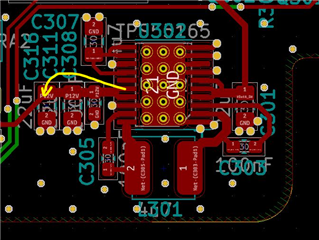

I have made a design per the webench recommendation to generate 12V out. Input is from a 3 cell Li Ion battery. Nominal 10.6V. Output measures 8.7 in one instance, 9 V in a second instance of the circuit no load. Vref measures 4.89V and connects to Vos_fb to output 12V. Why isn't it 12V?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.