Hello Expert,

Must we implement the Watchdog timer when limp home mode is not need?

If we disable the Warchdog timer,what happened if SPI is loss and MCU fail to communicate with the devise?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Expert,

Must we implement the Watchdog timer when limp home mode is not need?

If we disable the Warchdog timer,what happened if SPI is loss and MCU fail to communicate with the devise?

One more question, about the 8.3.2 Initialize Device with Watchdog Timer

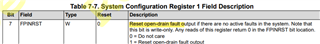

2. Write byte 0x10 to register 0x00. This will set bit D7 to 0 and reset the FLT indicator

------ How can we reset the FLT by setting D7 to 0? According to datasheet we should write 1 to D7 to reset this FLT

Implementing the watchdog timer is a system level determination. Without the watch dog timer then the device will operate based on its conditions and register settings. It will not do anything different until told to do so. If you lose SPI without watchdog timer, then it will run as it is indefinitely.

writing 0x10 to address 0x00 will not reset the FLT pin. It will enable the watch dog timer only. There is a typo in section 8.3. If you want to set the watch dog timer and clear the FLT pin then you need to write 0x90.

If you want to turn off watch dog timer and clear FLT pin then write 0x80

Always follow the register map vs text in sections of the datasheet. Sorry about the typo. It will be fixed in the next revisions of the datasheet.

-fhoude

Dear expert,

Thank you for your information! So shall we reset the FLT by writing D7 to 1 when power on and in the initialization? Or it will reset by itself when power on?

by default FLT pin is set high (FLT pin pulled low) and must be reset by sending a write of 1 to that bit. That was intentional and must be parts of your initialization routine.