Other Parts Discussed in Thread: TIDA-010208

Hello TI Team,

We are designing BMS with BQ76952. And we are confused about the connection the diode in DSG circuit of BQ76952.

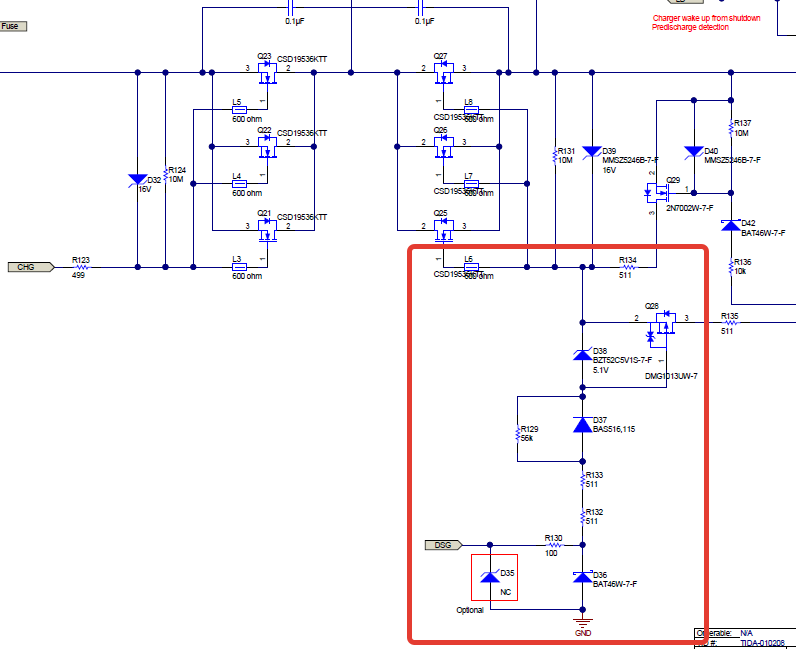

The schematic of TIDA-010208 10s–16s Battery Pack Reference With Accurate Cell Measurement and High-Side MOSFET Control has follows recommendation to connect DSG pin of BQ76952 to discharge MOSFET:

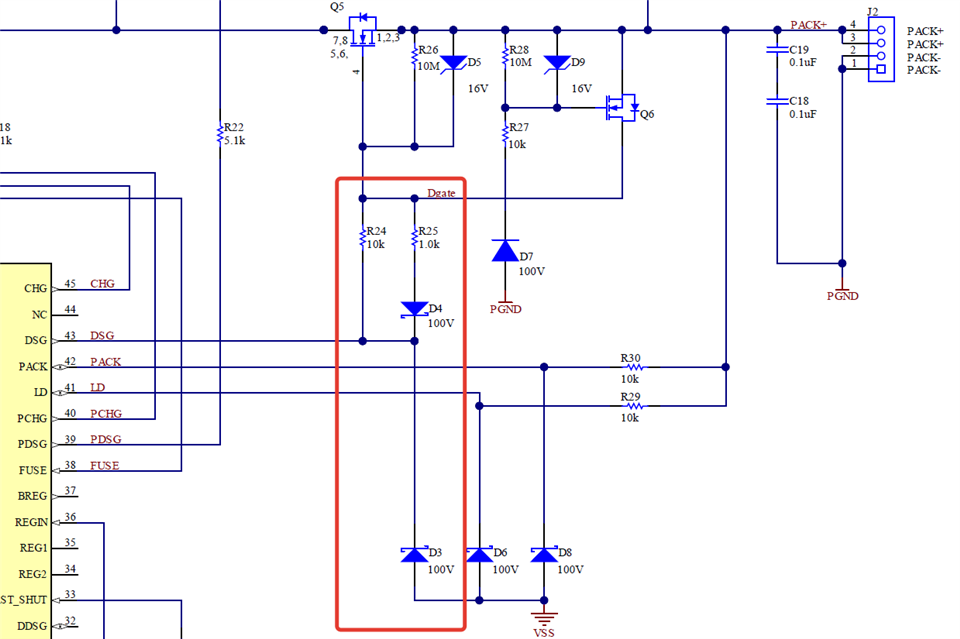

But in the Application Note sluaa09a Multiple FETs with the BQ769x2 Battery Monitors in the Figure 1-1. Typical 7S Series FET Schematic we found out different recommendations to connect the same DSG pin:

It seems that diode D37 in the schematic of TIDA-010208 has opposite direction than the diode D4 in the schematic in the Application Note sluaa09a Multiple FETs with the BQ769x2 Battery Monitors.

May we ask you to explain us what direction of connection of that diode is better?