Hi,

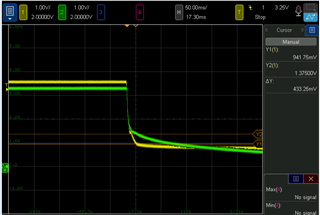

Currently we are using TLV70033 in our design. During power down, there is a small moment (<100ms) where the Vout>Vin by ~0.45V as below.

Question: Will the LDO damage if Vout>Vin+0.3V for such short period of time? Please advise.

Vin=yellow, Vout=green.