Other Parts Discussed in Thread: TPS7A85

Hello everyone,

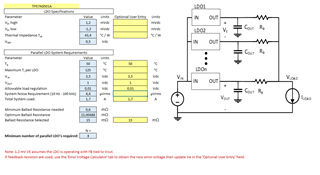

I was pleased to see that the excel spreadsheet for calculating parallel LDOs has been updated with the addition of the TPS7A85A and the calculator for external resistors. Thank you!

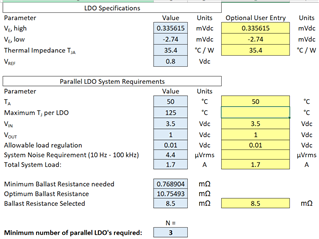

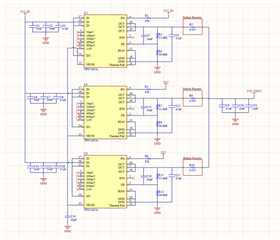

Now I would like to ask your help to verify the following desing:

1) In a previous thread (https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1189469/tps7a85-serial-vs-parallel-design-for-high-reliability) TPS7A85A was recommended over the TPS7A85, but the TPS7A85A seems to have worse thermal characteristics...it's right? Did I miss something?

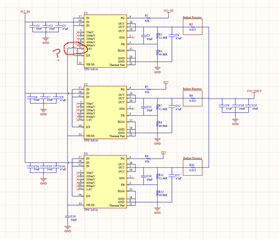

2) I connected all NR/SS pins together (like in TIDA-01232), is that correct?

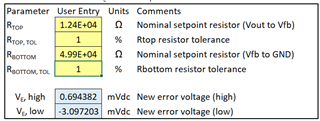

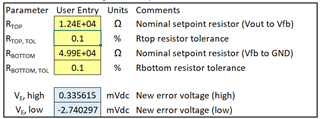

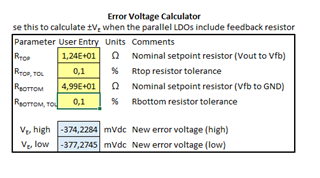

3) if I use external resistors calculator (with Rtop 12.4k and Rbot 49.9k, so Vout=1) i have Vₑ high = -374 and Vₑ low = -377 (??), is this correct?

Thanks in advance!

Antonio