Hello,

We have been experiencing an unexpected behavior on one UCD9090-Q1 device.

During the P3V3 power-up, the FPWM7 GPIO11 of that device does not stay low as it would be expected from the datasheet.

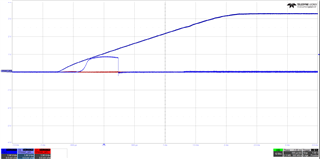

The screenshot below illustrates the issue:

This screenshot displays the 3V3 power-up, the FPWM_GPIO11 (issue) and FPWM_GPIO12 (no issue).

We don't have the issue on our other boards so it seems to be specific to that particular device which raises concerns as this is not something we would expect.

As this already been experienced before either by TI or by TI's customers ?

Best regards,

Clément