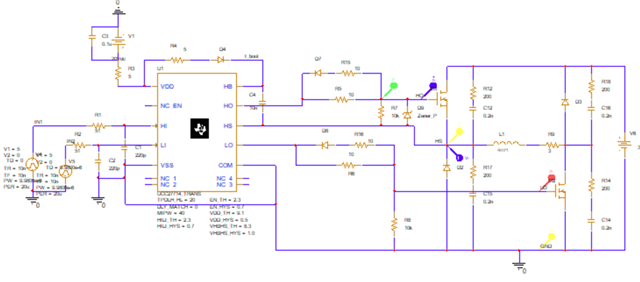

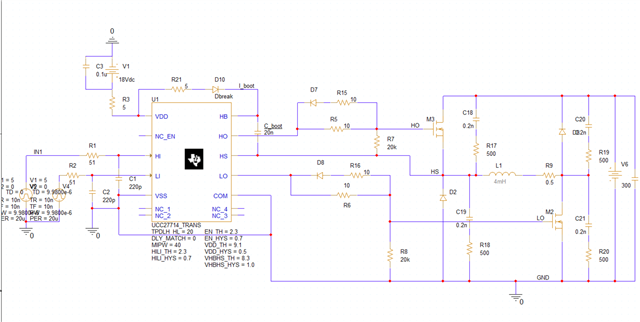

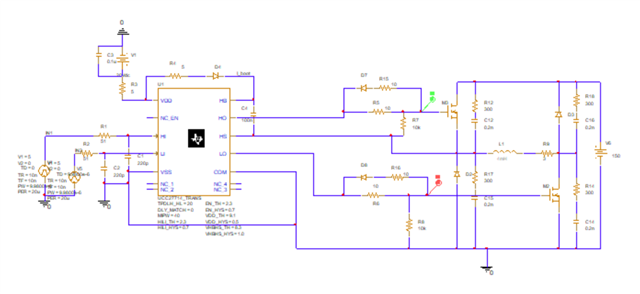

Figure 1 is my simulation schematic

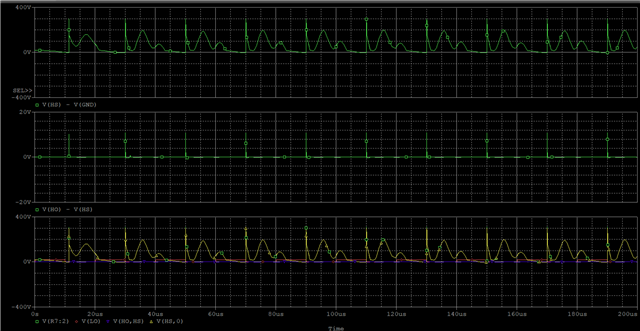

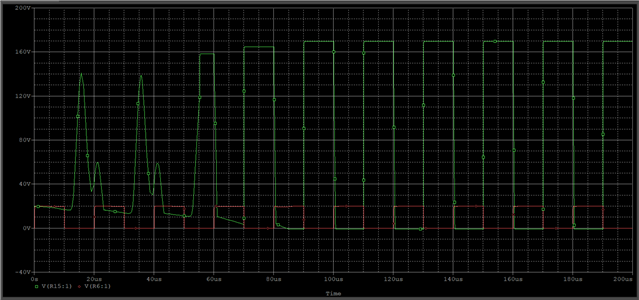

Figure 2 shows the HO and LO output waveforms

Figure 3 shows the driving waveforms of HO and LO when I increase the H-bridge supply voltage to 300V

I want to drive load L1 through the H-bridge, but the drive waveform is distorted on the high side.

At the same time, I wanted a faster current response, so when I tried to increase the H-bridge supply voltage, the drive waveform on the high side was completely deformed.

What adjustments I need to make,Hope for your help.