Team,

Can you please help with the below issue customer is facing:

We are currently implementing a SW driver for TPS65313-Q1.

There are some behaviors that do not seem to follow the datasheet specification and that we do not understand.

Can you please help with the below:

The TPS65313-Q1 is initialized and then cyclically supplied with watchdog responses and correct ESM toggles until one successfully enters the

Active State and the Enable Drive(ENDRV) is correctly activated.

All status information is read cyclically.

In the Active State, Lbist / Abist should now also be executed cyclically (which works alone in each case).

As soon as Lbist and Abist are executed together (with an offset of >1000ms to each other), an executed Lbist after an Abist generates error bits

but in the Abist error registers (SAFETY_ABIST_ERR_STAT5 contains value 0x1b, SAFETY_ABIST_ERR_STAT6 contains value 0x02).

- why are these bits set although the last abist was >1000ms ago and the abist itself completed successfully without error bits?

unfortunately i did not find any information about this in the datasheet.

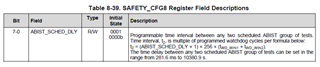

Regarding the Abist, an Abist is started over all groups (Group 1,2,3,4) at the same time. The Lbist is executed as follows: SAFETY_LBIST_CTRL is set to 0x1F, after >500ms SAFETY_LBIST_CTRL is set to 0x20 to test it itself.

I.e. the sequence is as follows :

Lbist -> 500ms -> Lbist Selftest --> Lbist pass, no problems --> 1000ms --> Abist --> Abist pass, no problems --> 1000ms --> Lbist --> Abist Register Faulty.

When Abist Group 4 is not running with, the behavior with bits set in SAFETY_ABIST_ERR_STAT does not occur.

Furthermore I found out that with the Lbist execution the bit EE_CRC_ERR in register SAFETY_ERR_STAT1 is always set.

Also for this I could not find anything in the datasheet.

Since I already found some places in the datasheet that are inconsistent or wrong, possibly some information could be missing in this case too.

Can you please clarify the behaviors described above?

Thanks in advance!

A.