Hi team,

I have a question.

Section 8.3.3 explains that when the MR pin is set to the Low level, the reset pin is also set to the Low level. In this case, will WDI monitoring be ignored and either t_WC or t_WO cleared to 0?

Best Regards,

Shoji

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

I have a question.

Section 8.3.3 explains that when the MR pin is set to the Low level, the reset pin is also set to the Low level. In this case, will WDI monitoring be ignored and either t_WC or t_WO cleared to 0?

Best Regards,

Shoji

Hi Yuya,

The RESET output is asserted when VDD voltage is below the monitored threshold or MR pin voltage is lower than threshold.

WDO output is asserted only when watchdog timer error is detected.

So RESET has higher priority than WDO error. If RESET is asserted when WDO is asserted, the device deasserts the WDO pin and watchdog is disabled until RESET pin is deasserted and startup delay frame is terminated.

And the device resumes watchdog related functionality only after the supply is stable and the tD time duration has elapsed.

Best Regards,

Sila Atalar

Hi Sila,

Thank you for your reply. I'd like to confirm three points.

watchdog is disabled

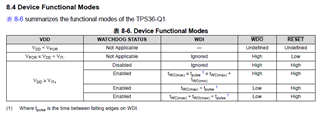

For WDI, WDI is ignored as this table shows, right?

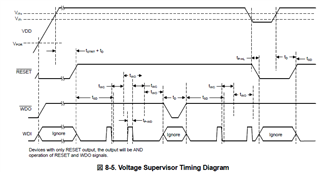

As far as I saw this diagram, MR pin is behaves as if it was V_DD because t_WC starts after t_D and t_SD terminated, right?

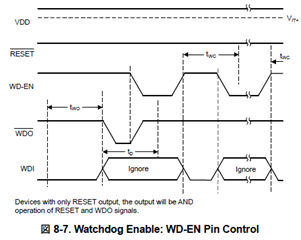

The difference between WD_EN and MR is whether it contains t_SD, right?

Best Regards,

Shoji

Hi Yuya,

1) For WDI, WDI is ignored as this table shows, right?

2) As far as I saw this diagram, MR pin is behaves as if it was V_DD because t_WC starts after t_D and t_SD terminated, right?

3) The difference between WD_EN and MR is whether it contains t_SD, right?

Best Regards,

Sila Atalar