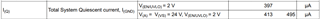

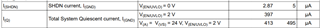

What is the typical and maximum quiescent current in the following two scenarios:

1. VBATT = 12V, VA=0V, VOUT=0V, EN/UVLO=0V, VC =0V, VS=VSNS=VSW - fed from VBATT via10k

2. VBATT = 24V, VA=0V, VOUT=0V, EN/UVLO=0V, VC =0V, VS=VSNS=VSW - fed from VBATT via10k

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.