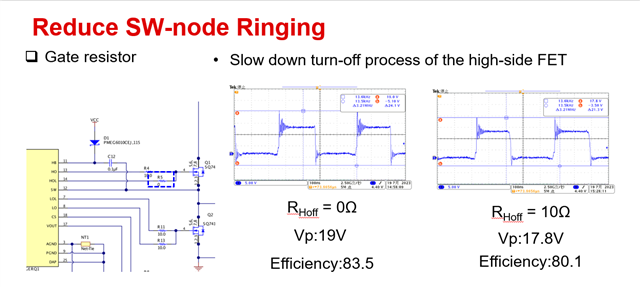

I increased the HS shut down resistor, why can I also reduce SW ringing.IS SW ring be related to the High side Mosfet shutdown speed?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.