I have followed the sequence described in the flowdiagram in the HOST technical manual and have initiated and completed the patch burst download and the download has been acknowlaged. But when i write the PBMc command do i get that the ac indicated data size is 0 and the calculated CRC is 0, and the ac fail code is 0. So I have some questions

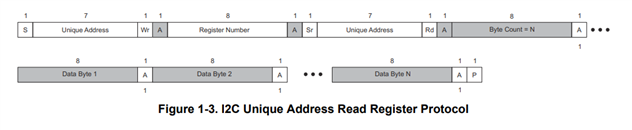

- the readsequence is described as address-register-byte count-data0-data1-...-dataN. But the patch download has no spesified register so should the sequence then be address-byte count-data0-...-datan or should it be address-byte0-...-byteN?

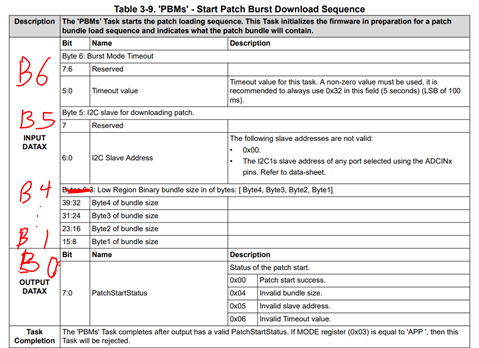

The second question is regarding starting the patch download with the PBMs command, because i figured that I needed to have the address in register 4 and the timeout value in register 5.

Is it correct that the data bundle size should be in register 0-3 or should it be in register 1-3 as register 0 is also used for outputing data after 4CC commands?