Other Parts Discussed in Thread: TDA4VM-Q1

Hello TI experts,

We are doing temperature cycle tests with our custom boards and find TPS6594 output abnormally. Some information is for you as below.

->The temperature range is from -40°~+85°。 We have reproduced this failure several times. Most of them are in low temperatue.

->Our SOC is TDA4VM-Q1 and we use PDN_0C power solution. That means we use TPS65941213 and TPS65941211.

->When this failure occurs, the test results of PMIC output are as below.

| Voltage/V | |||

| VSYS_3V3 | 3.3077 | ||

| PMIC_A | VDD_CPU_0V8 | BUCK123 | 0.0000 |

| VDD_MCU_0V85 | BUCK4 | 0.0000 | |

| VDD_PHYIO_1V8 | BUCK5 | 0.0031 | |

| VDD1_LPDDR4_1V8 | LDO1 | 0.0031 | |

| VDD_MCUIO_1V8 | LDO2 | 0.0001 | |

| VDA_DLL_0V8 | LDO3 | 0.0001 | |

| VDA_MCU_1V8 | LDO4 | 0.046 | |

| VRTC_LEOA_1V8 | Internal LDOs | 1.8030 | |

| VINT_LEOA_1V8 | Internal LDOs | 1.8003 | |

| PMIC_B_ENABLE | 1.7520 | ||

| PMIC_B | CORE_0V8 | BUCK1234 | 0.0000 |

| RAM_0V85 | BUCK5 | 0.0000 | |

| USB_3V3 | LDO2 | 0.0001 | |

| VDDIO_1V8 | LDO3 | 0.000 |

->when this failure occurs, I try to get the access to I2C with an external I2C tool but failed. Maybe PMIC's I2C can not work at that time. However, I dump the registers before this failure occurs and atteched.

Slave Address Register Address Register Name Register Value

0x48 1h DEV_REV 82

0x48 2h NVM_CODE_1 13

0x48 3h NVM_CODE_2 4

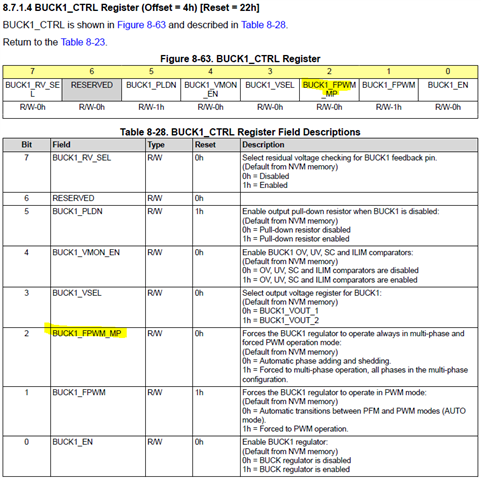

0x48 4h BUCK1_CTRL 31

0x48 5h BUCK1_CONF 2B

0x48 6h BUCK2_CTRL 20

0x48 7h BUCK2_CONF 2B

0x48 8h BUCK3_CTRL 30

0x48 9h BUCK3_CONF 2D

0x48 Ah BUCK4_CTRL 31

0x48 Bh BUCK4_CONF 2B

0x48 Ch BUCK5_CTRL 31

0x48 Dh BUCK5_CONF 1B

0x48 Eh BUCK1_VOUT_1 41

0x48 Fh BUCK1_VOUT_2 37

0x48 10h BUCK2_VOUT_1 37

0x48 11h BUCK2_VOUT_2 37

0x48 12h BUCK3_VOUT_1 FD

0x48 13h BUCK3_VOUT_2 FD

0x48 14h BUCK4_VOUT_1 41

0x48 15h BUCK4_VOUT_2 41

0x48 16h BUCK5_VOUT_1 B2

0x48 17h BUCK5_VOUT_2 B2

0x48 18h BUCK1_PG_WINDOW 1B

0x48 19h BUCK2_PG_WINDOW 1B

0x48 1Ah BUCK3_PG_WINDOW 3F

0x48 1Bh BUCK4_PG_WINDOW 1B

0x48 1Ch BUCK5_PG_WINDOW 1B

0x48 1Dh LDO1_CTRL 31

0x48 1Eh LDO2_CTRL 31

0x48 1Fh LDO3_CTRL 31

0x48 20h LDO4_CTRL 31

0x48 / 0

0x48 22h LDORTC_CTRL 0

0x48 23h LDO1_VOUT 38

0x48 24h LDO2_VOUT 38

0x48 25h LDO3_VOUT 10

0x48 26h LDO4_VOUT 38

0x48 27h LDO1_PG_WINDOW 1B

0x48 28h LDO2_PG_WINDOW 1B

0x48 29h LDO3_PG_WINDOW 1B

0x48 2Ah LDO4_PG_WINDOW 1B

0x48 2Bh VCCA_VMON_CTRL 21

0x48 2Ch VCCA_PG_WINDOW 3F

0x48 31h GPIO1_CONF 20

0x48 32h GPIO2_CONF 40

0x48 33h GPIO3_CONF 58

0x48 34h GPIO4_CONF C8

0x48 35h GPIO5_CONF 29

0x48 36h GPIO6_CONF 28

0x48 37h GPIO7_CONF 38

0x48 38h GPIO8_CONF 78

0x48 39h GPIO9_CONF 1

0x48 3Ah GPIO10_CONF D8

0x48 3Bh GPIO11_CONF 43

0x48 3Ch NPWRON_CONF 19

0x48 3Dh GPIO_OUT_1 0

0x48 3Eh GPIO_OUT_2 1

0x48 3Fh GPIO_IN_1 40

0x48 40h GPIO_IN_2 0F

0x48 41h RAIL_SEL_1 5A

0x48 42h RAIL_SEL_2 96

0x48 43h RAIL_SEL_3 5

0x48 44h FSM_TRIG_SEL_1 1E

0x48 45h FSM_TRIG_SEL_2 1

0x48 46h FSM_TRIG_MASK_1 55

0x48 47h FSM_TRIG_MASK_2 55

0x48 48h FSM_TRIG_MASK_3 15

0x48 49h MASK_BUCK1_2 0

0x48 4Ah MASK_BUCK3_4 0

0x48 4Bh MASK_BUCK5 0

0x48 4Ch MASK_LDO1_2 0

0x48 4Dh MASK_LDO3_4 0

0x48 4Eh MASK_VMON 0

0x48 4Fh MASK_GPIO1_8_FALL FF

0x48 50h MASK_GPIO1_8_RISE FF

0x48 51h MASK_GPIO9_11 3F

0x48 52h MASK_STARTUP 11

0x48 53h MASK_MISC 2

0x48 54h MASK_MODERATE_ERR 20

0x48 56h MASK_FSM_ERR 0

0x48 57h MASK_COMM_ERR 0

0x48 58h MASK_READBACK_ERR 0

0x48 59h MASK_ESM 3F

0x48 5Ah INT_TOP 0

0x48 5Bh INT_BUCK 0

0x48 5Ch INT_BUCK1_2 0

0x48 5Dh INT_BUCK3_4 0

0x48 5Eh INT_BUCK5 0

0x48 5Fh INT_LDO_VMON 0

0x48 60h INT_LDO1_2 0

0x48 61h INT_LDO3_4 0

0x48 62h INT_VMON 0

0x48 63h INT_GPIO 0

0x48 64h INT_GPIO1_8 0

0x48 65h INT_STARTUP 0

0x48 66h INT_MISC 0

0x48 67h INT_MODERATE_ERR 0

0x48 68h INT_SEVERE_ERR 0

0x48 69h INT_FSM_ERR 0

0x48 6Ah INT_COMM_ERR 0

0x48 6Bh INT_READBACK_ERR 0

0x48 6Ch INT_ESM 0

0x48 6Dh STAT_BUCK1_2 0

0x48 6Eh STAT_BUCK3_4 0

0x48 6Fh STAT_BUCK5 0

0x48 70h STAT_LDO1_2 0

0x48 71h STAT_LDO3_4 0

0x48 72h STAT_VMON 0

0x48 73h STAT_STARTUP 2

0x48 74h STAT_MISC 0

0x48 75h STAT_MODERATE_ERR 0

0x48 76h STAT_SEVERE_ERR 0

0x48 77h STAT_READBACK_ERR 0

0x48 78h PGOOD_SEL_1 0

0x48 79h PGOOD_SEL_2 0

0x48 7Ah PGOOD_SEL_3 0

0x48 7Bh PGOOD_SEL_4 0

0x48 7Ch PLL_CTRL 0

0x48 7Dh CONFIG_1 0

0x48 7Eh CONFIG_2 0

0x48 80h ENABLE_DRV_REG 0

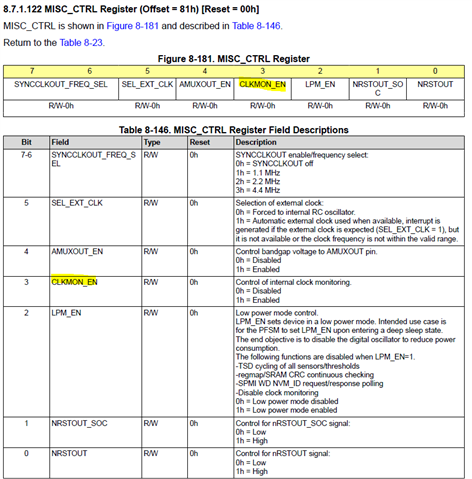

0x48 81h MISC_CTRL 1B

0x48 82h ENABLE_DRV_STAT 6

0x48 83h RECOV_CNT_REG_1 0

0x48 84h RECOV_CNT_REG_2 0F

0x48 85h FSM_I2C_TRIGGERS 0

0x48 86h FSM_NSLEEP_TRIGGERS 3

0x48 87h BUCK_RESET_REG 0

0x48 88h SPREAD_SPECTRUM_1 0

0x48 8Ah FREQ_SEL 0

0x48 8Bh FSM_STEP_SIZE 0B

0x48 8Ch LDO_RV_TIMEOUT_REG_1 FF

0x48 8Dh LDO_RV_TIMEOUT_REG_2 FF

0x48 8Eh USER_SPARE_REGS 0

0x48 8Fh ESM_MCU_START_REG 0

0x48 90h ESM_MCU_DELAY1_REG 0

0x48 91h ESM_MCU_DELAY2_REG 0

0x48 92h ESM_MCU_MODE_CFG 0

0x48 93h ESM_MCU_HMAX_REG 0

0x48 94h ESM_MCU_HMIN_REG 0

0x48 95h ESM_MCU_LMAX_REG 0

0x48 96h ESM_MCU_LMIN_REG 0

0x48 97h ESM_MCU_ERR_CNT_REG 0

0x48 98h ESM_SOC_START_REG 0

0x48 99h ESM_SOC_DELAY1_REG 0

0x48 9Ah ESM_SOC_DELAY2_REG 0

0x48 9Bh ESM_SOC_MODE_CFG 0

0x48 9Ch ESM_SOC_HMAX_REG 0

0x48 9Dh ESM_SOC_HMIN_REG 0

0x48 9Eh ESM_SOC_LMAX_REG 0

0x48 9Fh ESM_SOC_LMIN_REG 0

0x48 A0h ESM_SOC_ERR_CNT_REG 0

0x48 A1h REGISTER_LOCK 0

0x48 A6h MANUFACTURING_VER 8

0x48 A7h CUSTOMER_NVM_ID_REG 0

0x48 ABh SOFT_REBOOT_REG 0

0x48 B5h RTC_SECONDS 0

0x48 B6h RTC_MINUTES 0

0x48 B7h RTC_HOURS 0

0x48 B8h RTC_DAYS 1

0x48 B9h RTC_MONTHS 1

0x48 BAh RTC_YEARS 0

0x48 BBh RTC_WEEKS 0

0x48 BCh ALARM_SECONDS 0

0x48 BDh ALARM_MINUTES 0

0x48 BEh ALARM_HOURS 0

0x48 BFh ALARM_DAYS 0

0x48 C0h ALARM_MONTHS 0

0x48 C1h ALARM_YEARS 0

0x48 C2h RTC_CTRL_1 0

0x48 C3h RTC_CTRL_2 E0

0x48 C4h RTC_STATUS 80

0x48 C5h RTC_INTERRUPTS 0

0x48 C6h RTC_COMP_LSB 0

0x48 C7h RTC_COMP_MSB 0

0x48 C8h RTC_RESET_STATUS 0

0x48 C9h SCRATCH_PAD_REG_1 0

0x48 CAh SCRATCH_PAD_REG_2 0

0x48 CBh SCRATCH_PAD_REG_3 0

0x48 CCh SCRATCH_PAD_REG_4 0

0x48 CDh PFSM_DELAY_REG_1 58

0x48 CEh PFSM_DELAY_REG_2 9D

0x48 CFh PFSM_DELAY_REG_3 0

0x48 D0h PFSM_DELAY_REG_4 0

Could you help analyze what errors have occurred in PMIC base on the information above? Thank you in advance.