I am developing a power supply with some surge protection in which I want the device to shut off when we see an inrush stay above 3A for a period of time the TPS switch should then only retry once the Enable line has been re-enabled by a 3.3v FPGA controller.

I am not confident my results in running the spice models as I have noticed the device will not restart between the lower voltage simulations (3.3V & 5V) compared to the 15v & 24v simulations when I run simulations with the with the same components & configuration.

To resolve this I have left floating the LDSTRT pin for the low voltage sims (<5v) but with the 15V and 24v simulations to get the same behaviour the LDSTRT must be grounded with a 0.1uF capacitor.

Without doing this I cannot re-enable the device with the ENUVLO pin.

Is it a requirement to place a smaller capacitor between ground for the lower voltage system? This is confusing as the calculation for CLDSTRT (Equation 23) does not use input voltage to derive handshake time.

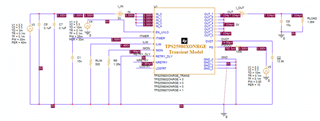

An example of the 24 and 3v Circuit can be seen below. Also somewhere else in the datasheet it mentions it should always be grounded with a capacitor.