Other Parts Discussed in Thread: LM5122, LM5122EVM-2PH, LM5122ZA

Hi TI Team,

We have designed and built a two-phase boost converter with the following operational parameters:

- Vin = 36-53VDC (48VDC Nominal)

- Vout = 60VDC

- Pout(continuous) = 250W

- Pout (100ms) ≥1kW

I'm able to share schematics/layout privately, as covered by our MNDA on file. Please let me know where I should send.

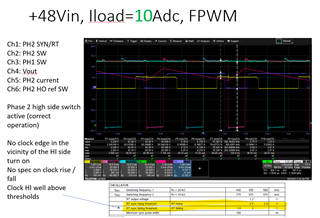

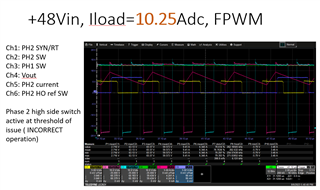

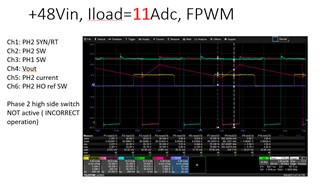

Our issue is that the slave device begins, around 10A of output current, to intermittently drop pulses. As we increase the current, it drops out entirely.

We checked the feedback loop and the components are correct. We also looked and saw that the timer cap is not being discharged (as would be the case in a hiccup mode event). Even so, we grounded the RES net shared between the two devices just to check, but the issue remained. Finally, we swapped out the part, and it the issue persisted.

One thing we noticed about the layout is that there was a polygon that was intended to connect the PGND pins on the 5122 back to the EP pad under the part (to join the AGND pin) and, for some reason, this was missing. They are missing on both the Master and the Slave devices, but the slave device is having the issue. We attempted to bring the AGND and the PGND together by placing a large shorting wire over top of the device. We then grounded that shorting wire to an adjacent ground plane.

We are also attempting to measure the LO output signal and noticing that the signal does not appear to be pulling down to ground (it's relatively constant across load- pulling down to 1-2VDC. This makes us wonder if the dead time block inside the IC is preventing the high side from turning on.

We've noticed a few other e2e posts in which other engineers were having issue with the slave controller's high-side device dropping out under increasingly heavy load, so we're wondering if there is a particular susceptibility to this phenomenon for a device operating as a slave device.