Hello, TI:

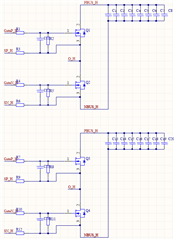

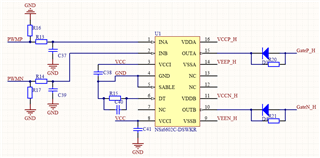

I use UCC21542 to drive a half bridge module, of which the schematics are presented at the end. Each arm of the bridge consists of two MOSFETs in parallel. The auxiliary power supply for each arm is 15V (isolated). A zener diode is used to generate +12V/-3V for the gate driver. That means VDD is 12V, VSS is -3V.

The MOSFET is NVH4L040N65S3F, the datasheet is attached.0815.MOSFET.pdf

1) The Qg_total of each mosfet is 160nc@10V. The switching frequency is 50kHz. So, the total power consumption to charge and discharge the mosfet is approximately 2*160e-9*1.5*15*50e3*2 = 0.72W. Is it correct? The external capactor between G-S is 100pF, which is ignorable.

2) The gate resistors consist of two parts: two separate 1Ω resistor are placed at the G terminal and S terminal of each mosfet; a common 1Ω resistor acts as another turn-on resistor while the diode is used to reduce the turn-off resistor. In this way, if the two MOSFETs are equalized as one, the equivalent turn-on resistor is 2Ω, while the turn-off resistor is 1Ω.

3) The internal gate resistor of each mosfet is 1.9Ω. Therefore, the equivalent internal gate-resistor is 0.95Ω.

4) I am somehow confused by the equations to calculate the power consumption of UCC21542, as provided by its datasheet. I guess the power consumption of UCC21542 should not have exceeded its limit.

However, when the DC-link bus voltage is increased to 150V while the load current is 30A DC. The UCC21542 is damaged but the MOSFETs are OK.

Could you please help to address my questions?

1) What is the most possible reason for the damage of UCC21542?

2) Does the power consumption exceed the limit of UCC21542?

3) Is it right to place resistors at both the G terminal and S terminal? I thought this should be necessary for paralleling two MOSFETs.

4) I will try to increase the external turn-on resistor, but I am not sure if this is the right solution.

Thanks and best regards.