Hi

I have some question about CL setting and Fault time behavior.

Q1. is it correct?

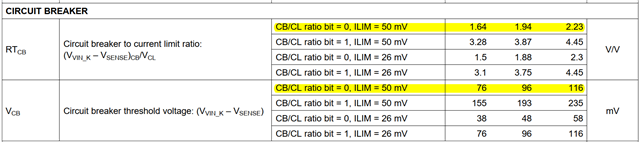

PIn setting: there are 2 CB value (1.94x or 3.87x current limit) ==> Base on CL pin connect to VDD or GND or leave floating

SMBUS setting: there are 4 CB value (1.94x, 3.87x, 1.88x, 3.75x current limit) ==> Base on register D9h bit[3], bit[4]

Original design is pin set (CL pin to VDD, Retry pin to VDD),

Is any side effect if we change to SMBUS setting (D9h: 24h) when we keep the circuit?

When D9h bit[2] set to 1, the LM5066i will ignore the external circuit. ==> Correct?

Icc, max = 11.11A

D9h: 24h (No retry, 50mV, 1.9x, SMBUS Setting)

==> Current Limit is 33.3A

CB is 64.6 = 33.3 x 1.94

is it correct?

Q2. Fault time behavior

when current limit threshold is reached and fault timer is active, Gate voltage is controlled to limit the current in MOSFET.

How to Gate control MOSFET?

Base on Figure 15, Gate pin will drop and latch in Fault Timeout Period. Vout will be?

if we set no retry, Will Gate pin have same behavior?

Thanks!

Penny