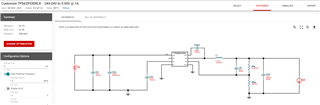

I'm modelling a buck converter based on TPS62933 chip in Webench Power Designer.

The input data is as follows: 24V in, 5V out, 0-1A output current, 1.2MHz output frequency. Everything else is in default state.

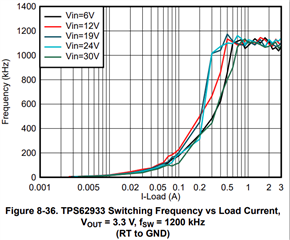

When then entering in "operation values" tab Vin = 24V and Iout from 0.23 to 0.375A, Power Designer outputs the resulting switching frequencies over 1.2MHz (up to 1.96MHz). When current goes from 0.375 to 0.376A, the frequency drops from 1.96 to 1.2 MHz in one step (I guess, it has something to do with min IL peak-to-peak value = 0.75A, like 0.375A is a half of it).

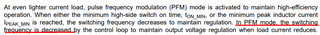

Nowhere in the datasheet I found mentions about conditions where switching frequency can go over the desired value, especially that much over (it can only be decreased by chip logic in PFM-mode due to frequency foldback).

If I choose 2 MHz as a desired switching frequency, the actual frequency shown goes over 2.4 MHz which is way bigger than absolute maximum 2.2 MHz frequency.

So is there a Power Designer model problem, or I'm missing something?

Thanks.

P.S. I can go for "simulation" mode, that often shows more expected results, than "customize" mode, however, this mode simulates only a few basic parameters, and completely misses some, like efficiency, power dissipation, junction temperature etc (which are present only in "customize" mode and are calculated based on the mentioned above values, so they are probably erroneous too).