Other Parts Discussed in Thread: CSD87350Q5D,

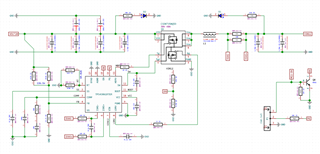

I'm designing a 12V21.8A input 20V12.5A output 96% efficiency boost power supply, using the MOS for the CSD87350Q5D power block.

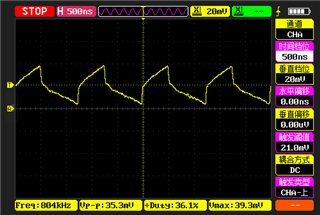

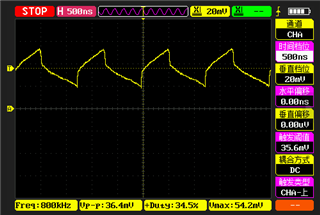

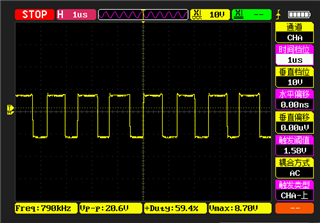

The design switching frequency is around 820kHz (actual 790kHz), the current limit is 2mR (35.6A at D=40%), the detailed calculation parameters are located at the end of the article.

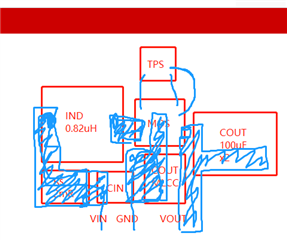

PCB layout ↓, all high current traces use 1x1mm copper strips to expand the current carrying.

The output capacitor is:

Calculated and practically used loop compensation parameters

R_COMP=27.17k(30K)

C_COMP=9.10n(10n)

C_HF=30.24p(33p)

These values passed the Webench power check and simulation.

However, the actual testing of this loop compensation parameter resulted in overcurrent protection.

|

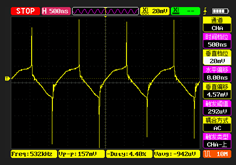

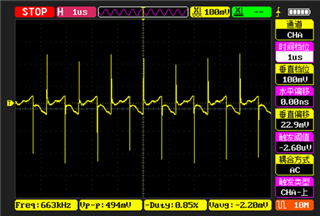

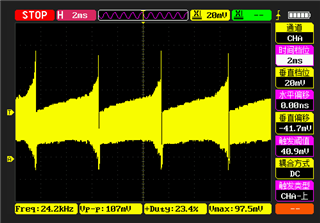

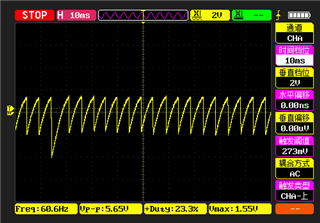

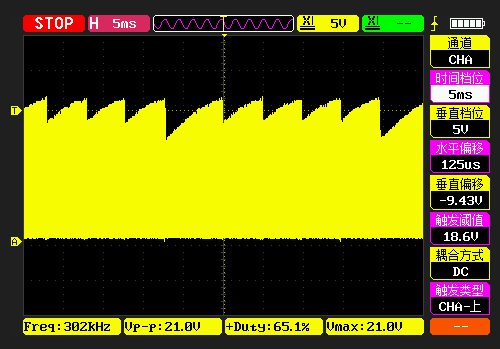

A 107mV peak appeared on the 2mR current detecting resistor (Fig. 1 below), a recharge appeared on the SS capacitor (Fig. 2 below), and the SW long time waveform (Fig. 3 below) |

|

|

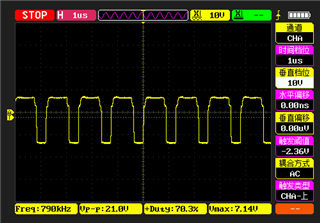

The HS control waveform, LS control waveform, and SW waveform, are all normal except that the overcurrent protection is triggered, but the duty cycle changes due to undervoltage caused by the current protection. |

|

If I change the COMP values to:

R_COMP=30K

C_HF=10n

C_COMP=33p

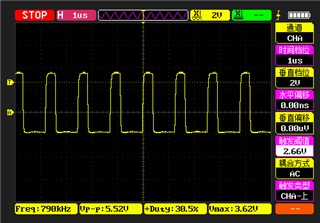

By swapping C_HF and C_COMP, the power supply can output 20V10A stably.

However, Webench warns that this compensation value fails the check, suggesting that the phase margin is too low.

|

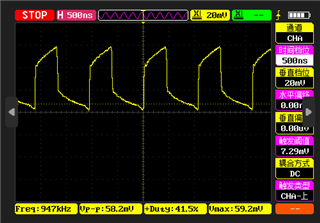

This is another test board pairing the C_COMP and C_HF current detection waveforms. The switching frequency is 940k, and the above problem also occurs when using the loop compensation parameters under theoretical calculations. There is only a 58mV peak on the 2mR current detecting resistor (Figure 1) |

|

I would like to inquire what causes this? And what to do to solve it.

Why is there a peak current of about 50A at 100mV detected current when using COMP component parameters near the theoretically calculated values?

As well as the fact that I am using a set of values that cannot be stabilized theoretically, yet I can maintain a stable 10A output?

Previously I also designed a test board for the TPS43061.

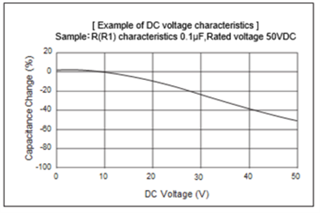

It had used a CKG57NX7R1H476M500JJ double layer capacitor,

two capacitors in parallel to get a low ESR output capacitor bank of 66uF 5mR or so, and an additional 330uF solid state capacitor to provide output current.

The output can be stabilized without triggering the overcurrent protection using the calculated COMP compensation parameters.

C_OUT_LIST = [

[11.6 * uF, 3 * mR],

[11.6 * uF, 3 * mR],

[3.3 * uF, 3 * mR],

[5 * uF, 20 * mR],

[100 * uF, 35 * mR],

[100 * uF, 35 * mR],

]

===== DESIGN =====

V IN = 12.00V [11.80V~12.30V]

I IN = 21.72A

POUT = 20V 12A

EMAX = 96.5%(-8.84W)

===== BOOST =====

Duty = 40% [38%~41%]

SW = 823kHz MAX:2357kHz

RT = 69.82kΩ

===== IND =====

L = 0.80uH(0.82)

I = 21.21A rms:21.31A peak:24.88A

RS = 2.00mΩ(<2.11mR) 2.59W

CURRENT LIMIT = 35.65A(>33.75A)

IND TD = 1.903W

===== MOS =====

I gd = 23.39mA

P COND = HS:1.339W LS:0.392W

P LOSS = SW:0.376W DT:2.238W

TDP = 4.344W

===== CAP =====

V IN RIPPLE = 37mV(60) 0.3%

C IN = 30uF(7.39)

V OUT RIPPLE = 26mV(200) 0.1%

C OUT = 232uF(31.13)

C OUT ESR = 0.90mΩ (6xCap)

C OUT I RIPPLE = 10.60 A

===== CONFIG =====

R FB HS = 226.50kΩ

R FB LS = 14.70kΩ

C BOOT MIN = 0.034uF

C SS MIN = 0.100uF

R UVLO HS = 47.00kΩ

R UVLO LS = 5.42kΩ

UVLO DIS:10.79V EN:11.61V

===== COMP =====

R COMP = 27.17kΩ

C COMP = 9.10nF

C HF = 30.24pF

===== Freq =====

Adc = 17.70V/V

f_Pmod = 0.43kHz

f_Zmod = 0.76MHz

f_RHPZ = 110.70kHz

f_co1 = 27.68kHz

f_co2 = 164.70kHz

f_co = 27.68kHz