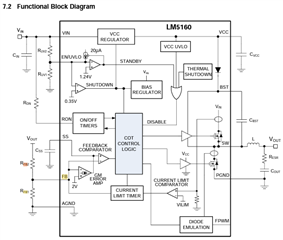

Other Parts Discussed in Thread: LM5160,

Dear TI team

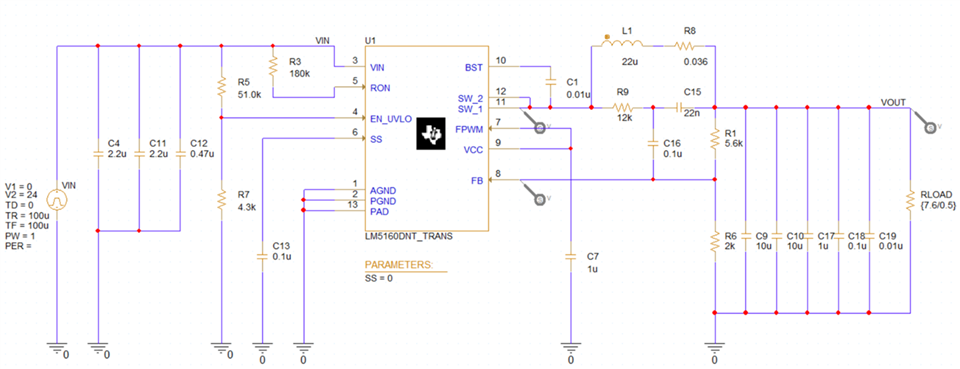

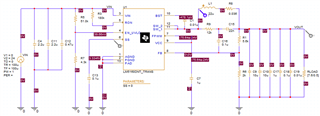

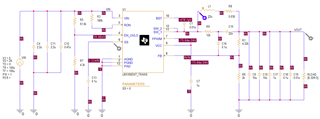

I'm running a simulation of the LM5160 on PSpice.

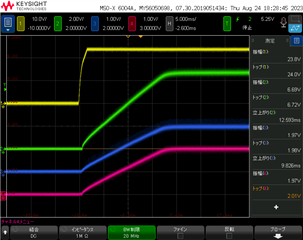

I was able to confirm that it basically works as intended.

However, there is one thing that bothers me, and I am contacting you.

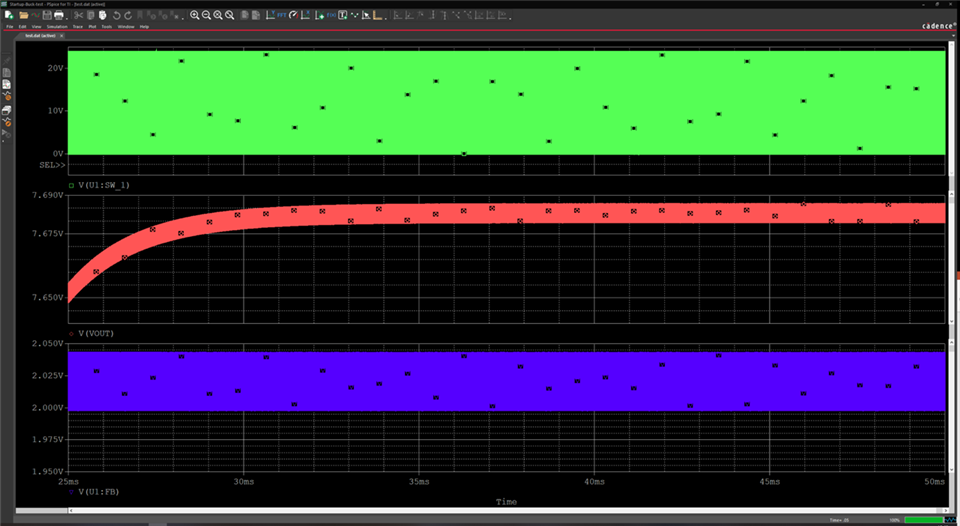

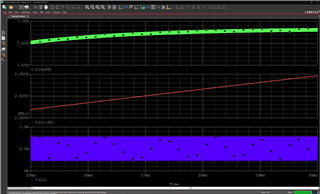

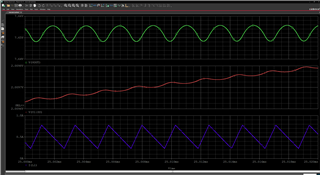

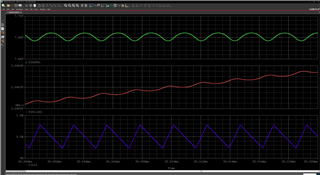

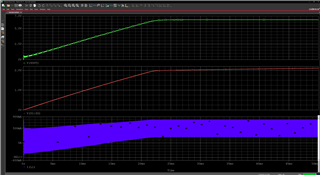

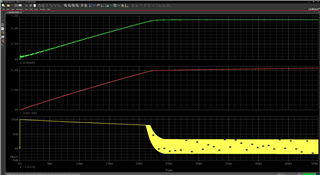

The bottom voltage of VFB stabilizes at 2.0V after the soft-start time has elapsed after power-on.

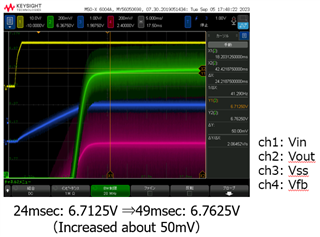

Therefore, I think that VOUT stabilizes at least at 25msec in the waveform below.

However, in the simulation results, the voltage seems to rise up to about 33msec.

Please let me know if you have any ideas as to why this is the case.

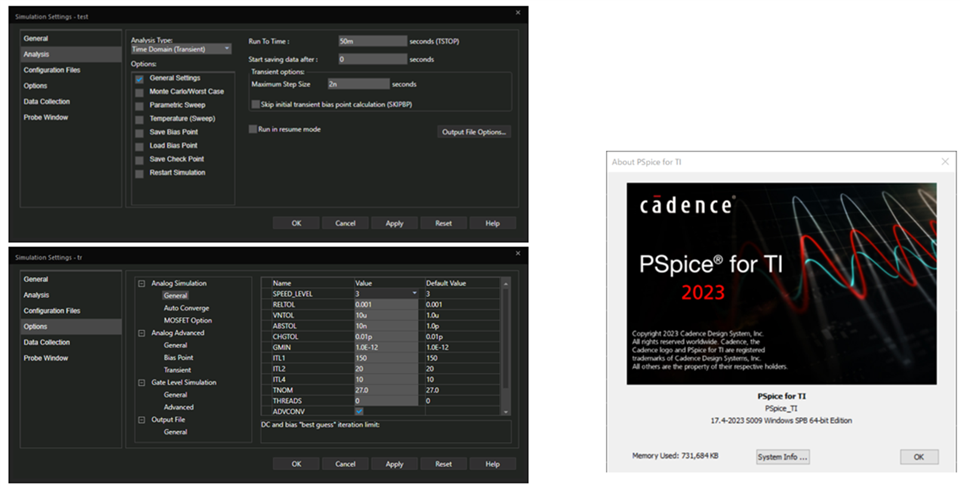

We will also send you the simulation settings and tool version just in case.

Best Regards,

Taroimo