Hello,

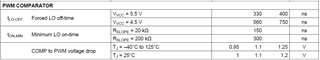

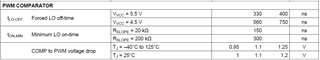

Considering your answer and thj following table in the datasheet of the LM5122 :

I understand that there is always a 330ns for example garanted for Toff when you have a big duty cycle.

Tanhk you

Biellmann cedrick

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

Considering your answer and thj following table in the datasheet of the LM5122 :

I understand that there is always a 330ns for example garanted for Toff when you have a big duty cycle.

Tanhk you

Biellmann cedrick

Hi Cedrick,

Yes, you are correct.

If you have any additional questions, or need help with your LM5122 design, please let us know.

Thanks and best regards,

Niklas

Hello Cedrick,

Niklas will come back to you by the end of the day.

Best regards,

Harry

Hi Cedrick,

Sorry for the delay.

I have no data on values between 4.5V and 5.5V VCC, and I cannot confirm that the max TLO_OFF time rises linear within this range.

In addition, the 400ns and 750ns are the worst case maximum values, which are higher than the typical values seen in normal operation.

From a datasheet perspective, the worst case TLO_OFF time for 5V VCC is still 750ns, as there is no other data given.

In reality, your calculation with 575ns should be closer the actual maximum off-time.

The mean value at 5V VCC should also be around 445ns, so if you leave some margin and calculate your design with a max off-time of 600ns, the risk should be minimized.

Best regards,

Niklas