Hi Team,

Are there any data showing variation of ROL resistance?

It will need to estimate for sink.

Thanks, Koh

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Are there any data showing variation of ROL resistance?

It will need to estimate for sink.

Thanks, Koh

Hi Koh,

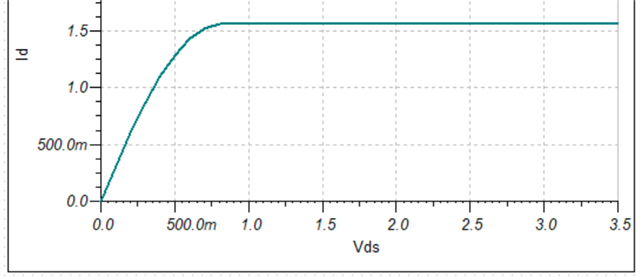

It is important to remember that the output is an NMOS. It acts like a resistor for low applied voltages and a current source (in parallel with a large resistor) for larger applied voltages. The resistance at low applied voltage is defined by the equation Id/Vds = µn*Cox*(W/L)*(Vgs-Vth). The saturation current is represented by Id= µn*Cox*(W/L)/2*(Vgs-Vth)^2.

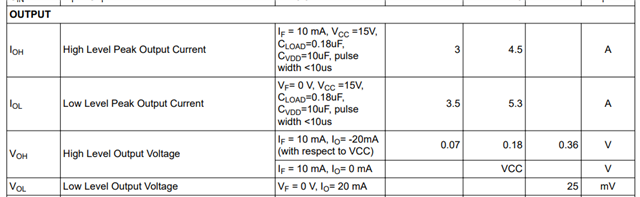

The on resistance typically has a linear positive temperature coefficient, and the saturation current is lower for higher temperatures.

The process variation effect is more limited because Vth= kT/q * ln(NaNd/ni^2).

Physical silicon model:

Min and Max datasheet range over temperature:

Best regards,

Sean