Hello,

I have a question about the TPS55288 IC.

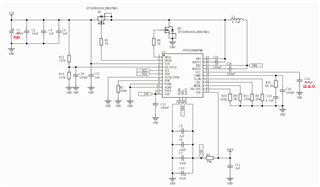

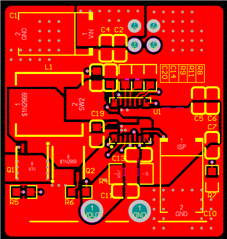

I have designed and made a schematic and PCB with the exact same components as the TPS55288EVM-045 Evaluation Board, and placed them on a much smaller PCB (about 25mm x 30mm) and I have noticed some unexpected behaviour:

When setting the output to 20 Volts via I2C and having no load on the output, the evaluation board draws 6mA of current and no components excerpt any noticeable amount of heat (recorded with FLIR thermal camera). When using the same component setup and the sending same I2C command to the custom made PCB, the current draw starts out at ~120mA and ramps down to ~16mA (again, no load), and the inductor on the board starts rapidly heating up to around 70 degrees C.

I have verified all resistance paths and connections to be the same as the Eval. board, tried different capacitor and inductor combinations, varied the switching frequency, nothing removes this parasitic draw.

Any help would be appreciated, thank you!