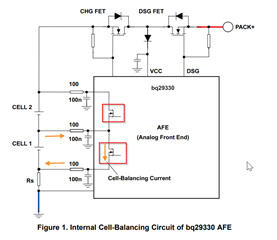

Section 8.3.5.5 mentions that "The device supports cell balancing by bypassing the current of each cell during charging or at rest. If the device's

internal bypass is used, up to 10 mA can be bypassed and multiple cells can be bypassed at the same time.

Higher cell balance current can be achieved by"

Is it more accurate to say 10mA at a minimum instead of "up to 10mA"

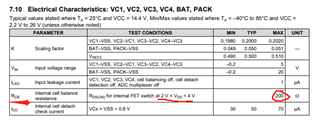

Section 7.10 "Electrical Characteristics: VC1, VC2, VC3, VC4, BAT, PACK" specifies that the internal balance FETs are 200ohm max, over a range of 2V to 4V.

So the balance current can really be 2V/200R (min of 10mA) but if we are nearing full charge, then 4V/200R = 20mA.

We probably care more about balance around the 3.65V area, so 18.25mA balance current.

Also, the FET res of 200ohm is MAX value over temp and processing, so the typical value of balance current should be much higher than 10mA.

Please let me know your feedback!

Thanks